## On Using the System Management Mode for Security Purposes

William Augusto Rodrigues de Souza

Thesis submitted to the University of London for the degree of Doctor of Philosophy

## On Using the System Management Mode for Security Purposes

Department of Mathematics Royal Holloway, University of London

Seeing much, suffering much and studying much are the three pillars of learning.

(Benjamin Disraeli)

### **Declaration of Authorship**

I, William Augusto Rodrigues de Souza, hereby declare that this thesis and the work presented in it is entirely my own. Where I have consulted the work of others, this is always clearly stated.

Signed:

(William Augusto Rodrigues de Souza)

Date:

### Summary

Computer systems are by design insecure and therefore are many security issues around them. So, security practitioners are always trying to enhance security and performing verification tasks to minimise the risk of potential threats become successful attacks. These tasks are usually performed by security tools.

Thus concepts as: isolation, privilege and view are important in the context of computer systems. Security tools must have good isolation, privilege and view of the system. Then, security tools must operate isolated, have high privilege and must have a global view of the system, but also good ability to view and act timely in its own environment to enhance the chances of success when performing their tasks and for not being hit by the problems they are trying to solve.

In this context, this research investigates the System Management Mode (SMM) in the context of Intel processors, current security tools capitalising on SMM and attacks and misuses of SMM to establish a set of requirements and then design a generic architecture for SMM-based security tools. That generic architecture is tested by building a proof of concept to measure the integrity of a file of the Xen hypervisor. This measurement is limited to the minimum necessary to prove the concept of the architecture.

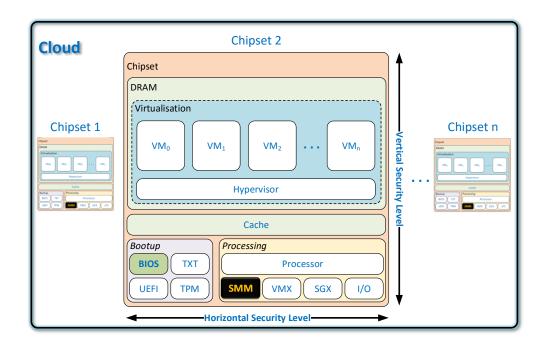

The problem context addressed is a cloud computing environment, comprising of one or more machines (chipsets). Each chipset hosts in its main memory (DRAM) a virtualised environment comprising of one manager virtual machine, one or more guest virtual machines and a hypervisor. We address our research investigation in two levels: the vertical and the horizontal security level. The vertical security level puts the problem in context, relating it to security issues on: cloud, chipset, memory, virtualisation layer and cache memory. The horizontal security level considers the research problem in its environment, relating it to security issues on components of the bootup process and the processor, such as: Intel VMX, TXT and SGX, BIOS and so on.

First, we investigate the SMM, its resources and components. Then, we analyse SMM-based security tools and the opportunities to improve them. We also analyse SMM attacks and how to thwart them. From the acquired knowledge, we establish a set of requirements to use SMM for security purposes. Having the requirements, we design a generic architecture for SMM-based security tools. To test the architecture, we build a proof of concept comprising of a module to probe chipsets and a SMM-based hypervisor integrity measurement tool.

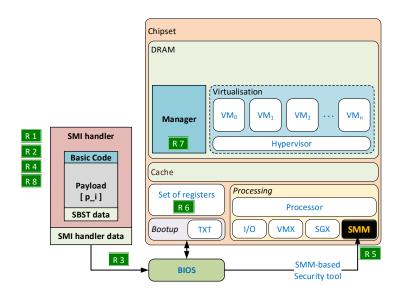

The implementation of that architecture was done in a proof of concept designed to have two modules: a manager and an agent. The manager module is used for learning about and researching on the target machine, as for probing, setting and clearing registers related to SMM. The manager can be used in the target machine or in a machine with the same chipset of the target machine. So, it can be deployed in main memory. The agent basically comprises of two parts: a basic code embodying management functions and a payload, where the security functions are implemented. So the use of a payload is what makes the architecture generic since any security task might be implemented and added in the agent by changing the payload.

We conclude that any security tool can capitalising on SMM resources provided that it meets the set of requirements established in this research: small, fast, persistent, cooperative, isolated, resistant, complete and SMI-independent (meaning that it can be started by any System management interruption, which occur in the chipset); and stick to the proposed generic architecture.

### Acknowledgments

My heartfelt thanks to my supervisor Dr. Allan Tomlinson for his guidance, encouragement, patience and dedication.

*I would like to also thank my examiners Professor William Buchanan and Professor Lorenzo Caballaro for taking the time to examine my thesis.*

I gratefully acknowledge all professors, specially Professors Chris Mitchell and Carlos Cid, colleagues and staff at ISG and at the Department of Mathematics for making my life easier and for all support, guidance and fruitful discussions.

I would like to also thank all support and encouragement I received from The Centre for Naval System Analysis of Brazilian Navy.

*I am also so grateful for all support and understanding received from my family.*

### Contents

| 1 | Intr                                                                                                  | oduction 1                                                                                                                                                                                                                                                                |

|---|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 1.1                                                                                                   | Motivation                                                                                                                                                                                                                                                                |

|   | 1.2                                                                                                   | Limits and Scope 3                                                                                                                                                                                                                                                        |

|   | 1.3                                                                                                   | Significance                                                                                                                                                                                                                                                              |

|   | 1.4                                                                                                   | Research Questions                                                                                                                                                                                                                                                        |

|   | 1.5                                                                                                   | Contribution                                                                                                                                                                                                                                                              |

|   | 1.6                                                                                                   | List of Publications                                                                                                                                                                                                                                                      |

|   | 1.7                                                                                                   | Overview of the Research 13                                                                                                                                                                                                                                               |

| 2 | Bac                                                                                                   | kground 15                                                                                                                                                                                                                                                                |

|   | 2.1                                                                                                   | Introduction                                                                                                                                                                                                                                                              |

|   | 2.2                                                                                                   | Definitions                                                                                                                                                                                                                                                               |

|   | 2.3                                                                                                   | Context and Technologies 19                                                                                                                                                                                                                                               |

|   | 2.4                                                                                                   | Environment and Technologies                                                                                                                                                                                                                                              |

|   | 2.5                                                                                                   | Data Integrity with Hash Functions                                                                                                                                                                                                                                        |

|   | 2.6                                                                                                   | Related work: System Executive Software Integrity Issues 40                                                                                                                                                                                                               |

|   | 2.7                                                                                                   | Discussion                                                                                                                                                                                                                                                                |

|   | 2.8                                                                                                   | Summary                                                                                                                                                                                                                                                                   |

|   |                                                                                                       |                                                                                                                                                                                                                                                                           |

| 3 | The                                                                                                   | System Management Mode (SMM) 45                                                                                                                                                                                                                                           |

| 3 | <b>The</b> 3.1                                                                                        | System Management Mode (SMM)45Introduction45                                                                                                                                                                                                                              |

| 3 |                                                                                                       |                                                                                                                                                                                                                                                                           |

| 3 | 3.1                                                                                                   | Introduction                                                                                                                                                                                                                                                              |

| 3 | 3.1<br>3.2                                                                                            | Introduction45Components46                                                                                                                                                                                                                                                |

| 3 | 3.1<br>3.2<br>3.3                                                                                     | Introduction45Components46SMM operation and relations54                                                                                                                                                                                                                   |

| 3 | 3.1<br>3.2<br>3.3<br>3.4                                                                              | Introduction45Components46SMM operation and relations54Security implementations using SMM58                                                                                                                                                                               |

| 3 | <ol> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>3.5</li> </ol>                           | Introduction45Components46SMM operation and relations54Security implementations using SMM58Launching attacks using SMM resources62                                                                                                                                        |

| 3 | <ol> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>3.5</li> <li>3.6</li> <li>3.7</li> </ol> | Introduction45Components46SMM operation and relations54Security implementations using SMM58Launching attacks using SMM resources62Discussion66                                                                                                                            |

|   | <ol> <li>3.1</li> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>3.5</li> <li>3.6</li> <li>3.7</li> </ol> | Introduction45Components46SMM operation and relations54Security implementations using SMM58Launching attacks using SMM resources62Discussion66Summary66                                                                                                                   |

|   | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br><b>Req</b>                                           | Introduction45Components46SMM operation and relations54Security implementations using SMM58Launching attacks using SMM resources62Discussion66Summary66uirements69                                                                                                        |

|   | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br><b>Req</b><br>4.1                                    | Introduction45Components46SMM operation and relations54Security implementations using SMM58Launching attacks using SMM resources62Discussion66summary66uirements69Introduction69                                                                                          |

|   | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br><b>Req</b><br>4.1<br>4.2                             | Introduction45Components46SMM operation and relations54Security implementations using SMM58Launching attacks using SMM resources62Discussion66Summary66uirements69Introduction69Threat model69                                                                            |

|   | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br><b>Req</b><br>4.1<br>4.2<br>4.3                      | Introduction45Components46SMM operation and relations54Security implementations using SMM58Launching attacks using SMM resources62Discussion66Summary66uirements69Introduction69Threat model69Assumptions72                                                               |

|   | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br><b>Req</b><br>4.1<br>4.2<br>4.3<br>4.4               | Introduction45Components46SMM operation and relations54Security implementations using SMM58Launching attacks using SMM resources62Discussion66summary66uirements69Introduction69Threat model69Assumptions72Requirements for using SMM for security purposes72             |

|   | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br><b>Req</b><br>4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6 | Introduction45Components46SMM operation and relations54Security implementations using SMM58Launching attacks using SMM resources62Discussion66Summary66uirements69Introduction69Threat model69Assumptions72Requirements for using SMM for security purposes72Discussion74 |

|     | 5.2<br>5.3<br>5.4<br>5.5<br>5.6 | Requirements Specification                                                    |      |

|-----|---------------------------------|-------------------------------------------------------------------------------|------|

| 6   | Imp                             | lementation and Evaluation - Manager Module and SBST                          | 105  |

|     | 6.1                             | Introduction                                                                  | 105  |

|     | 6.2                             | Functions in the Manager Module                                               | 108  |

|     | 6.3                             | Manager Module Computational Experiments                                      | 117  |

|     | 6.4                             | SBST Implementation and Evaluation                                            | 130  |

|     | 6.5                             | SBST Limits and Constraints                                                   | 132  |

|     | 6.6                             | Manager Limits and Constraints                                                |      |

|     | 6.7                             | Discussion                                                                    | 133  |

|     | 6.8                             | Summary                                                                       | 133  |

| 7   | Con                             | clusion                                                                       | 135  |

|     | 7.1                             | Directions for Future work                                                    | 137  |

|     | 7.2                             | Investigate the interaction of an <i>SBST</i> with technologies in the chipse | t137 |

|     | 7.3                             | Investigate the Impact of SMI Latency                                         |      |

|     | 7.4                             | Optimize the Proof of Concept Execution Time                                  |      |

|     | 7.5                             | Embed the Tool in a BIOS to Test It in a More Realistic Scenario              | 138  |

| Α   | Spec                            | ific SMM Registers                                                            | 139  |

|     |                                 | Chipset 1 Specific Registers                                                  |      |

|     |                                 | Chipset 2 System Management RAM Control register                              |      |

| Bil | bliog                           | raphy                                                                         | 155  |

## List of Figures

| Machine and Chipset 2                                |

|------------------------------------------------------|

| First set of machines used in the experiments        |

| Second set of Machines used in the experiments       |

| General architecture                                 |

| Security Context                                     |

| The Cloud Reference Model (figure from [131])        |

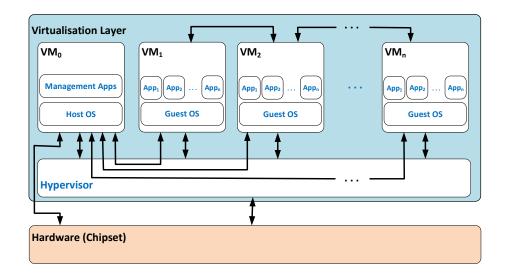

| Virtualisation Layer                                 |

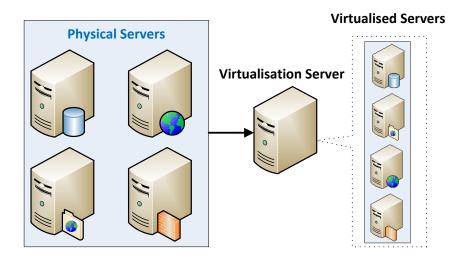

| Consolidation                                        |

| Containment                                          |

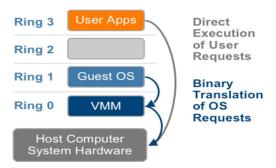

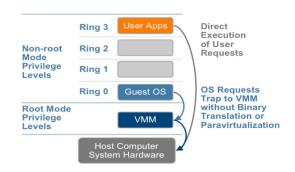

| Full virtualisation (figure from[140])28             |

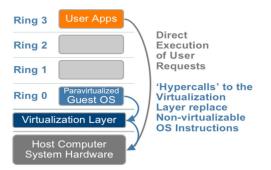

| Paravirtualisation (figure from [140])               |

| Hardware-assisted virtualisation (figure from [140]) |

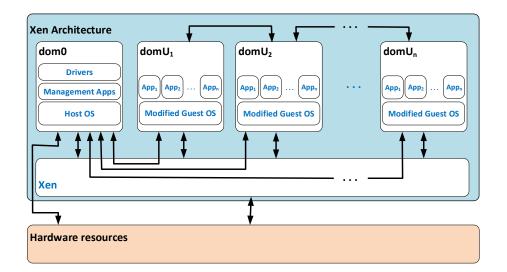

| Xen Architecture                                     |

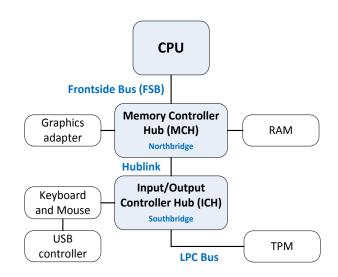

| Intel Hub Architecture, based on [57]                |

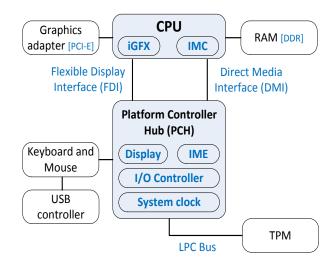

| The Intel Platform Controller Hub                    |

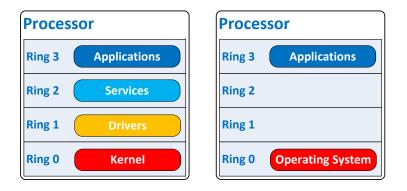

| Ring security scheme, based on [57] 35               |

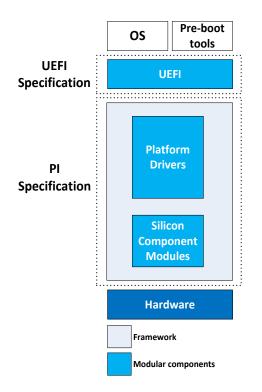

| The PI and UEFI layers, based on [153]               |

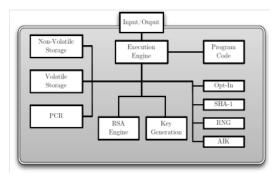

| TPM Overview (figure from [54]) [57]         39      |

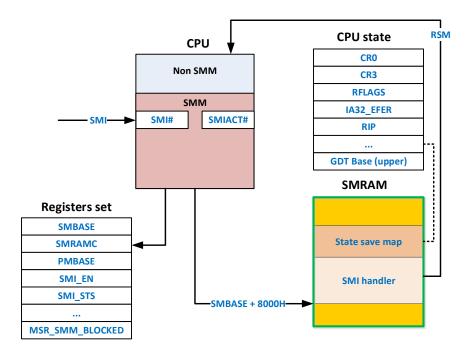

| SMM components                                       |

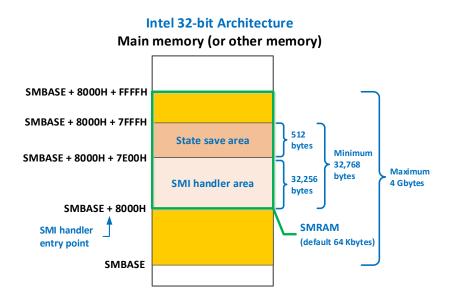

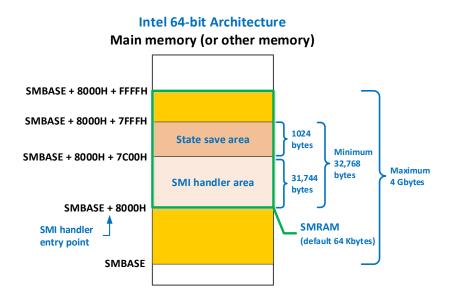

| SMRAM space for 32-bit machines                      |

| SMRAM space for 64-bit machines                      |

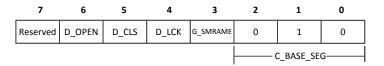

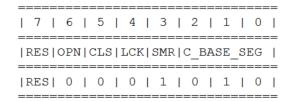

| SMRAM control register                               |

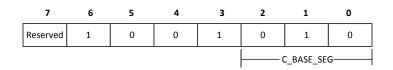

| SMRAMC state before SMRAM initialisation             |

| SMRAMC state after SMRAM initialisation              |

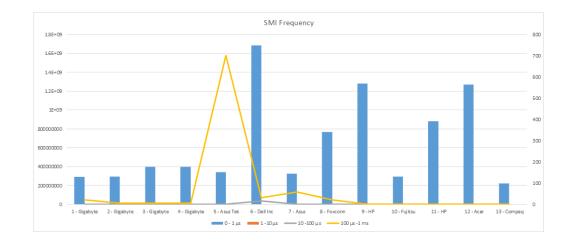

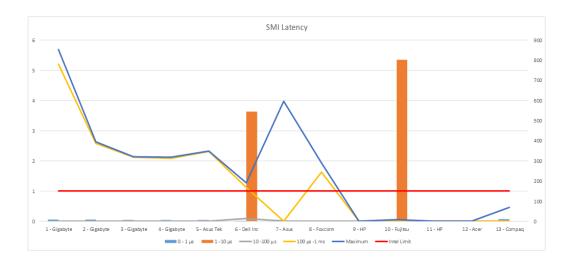

| SMI Frequency Graph 54                               |

| SMI Frequency Graph 55                               |

| Entering and exiting from SMM                        |

| Current SMM-based security tools architecture        |

| Threat model                                         |

| Mitigating threats                                   |

| General architecture                                 |

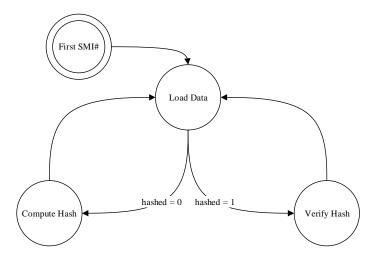

| Execution flow of the algorithms                     |

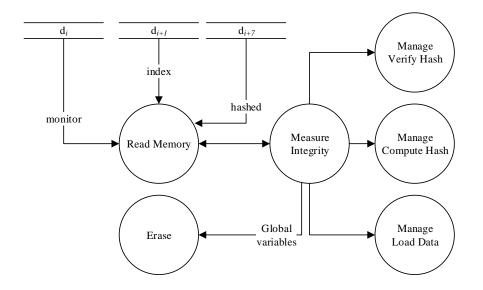

| Algorithm Measure Integrity    86                    |

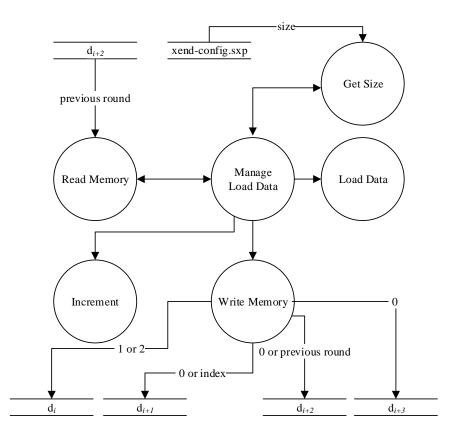

| Algorithm Manage Load Data                           |

|                                                      |

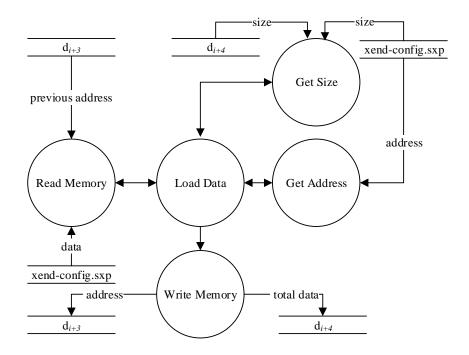

| 5.5  | Algorithm Load Data                                               | 92  |

|------|-------------------------------------------------------------------|-----|

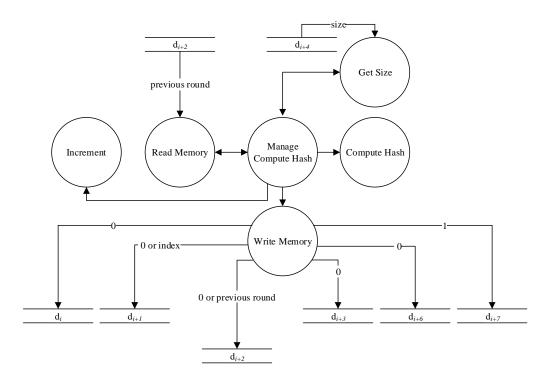

| 5.6  | Algorithm Manage Compute Hash                                     | 94  |

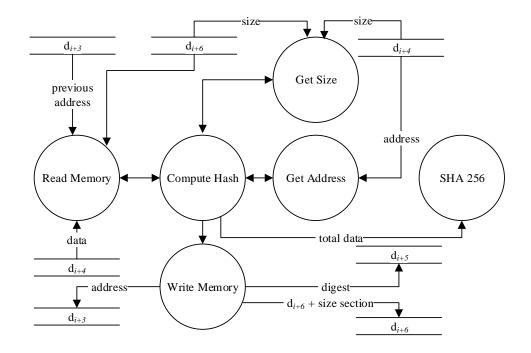

| 5.7  | Algorithm Compute Hash                                            | 96  |

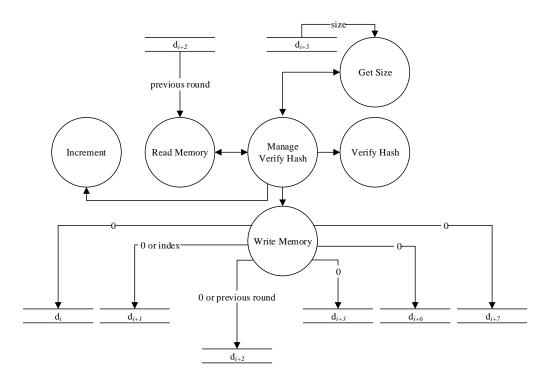

| 5.8  | Algorithm Manage Verify Hash                                      | 98  |

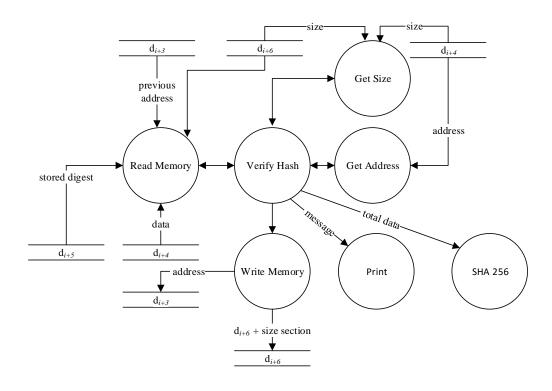

| 5.9  | Algorithm Verify Hash                                             | 101 |

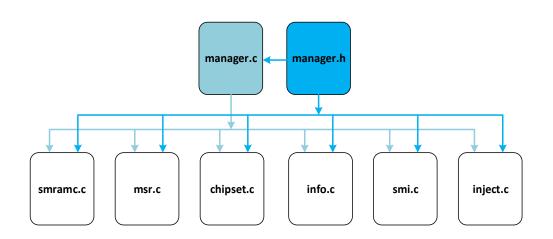

| 6.1  | Manager program files                                             | 107 |

| 6.2  | Manager main menu                                                 | 109 |

| 6.3  | SMRAMC status reported by the manager module for machine 12. Off- |     |

|      |                                                                   | 118 |

| 6.4  | SMRAMC status reported by the manager module for machines 1 to 5  |     |

|      | and 13. Offset 90H for machines 1 to 5 and 9dH for machine 13     | 119 |

| 6.5  | All PMBASE SMM Related Registers Status.                          | 120 |

| 6.6  | SMI_EN Register Status.                                           | 120 |

| 6.7  | SMLSTS Register Status.                                           | 121 |

| 6.8  | GPE0_EN Register Status.                                          | 123 |

| 6.9  | GPE0_STS Registers Status.                                        | 124 |

| 6.10 | ALT_GPI_SMI_EN Register Status.                                   | 125 |

| 6.11 |                                                                   | 126 |

|      | ALT_GPI_SMI_EN2 Register Status.                                  | 126 |

|      | ALT_GPI_SMI_STS2 Register Status.                                 |     |

|      | GEN_PMCON_1 Register Status.                                      |     |

|      |                                                                   |     |

## List of Tables

| 1.1        | Main SMM-Based security tools (SBST)                                       | 7      |

|------------|----------------------------------------------------------------------------|--------|

| 2.1        | Intel Chipsets                                                             | 1      |

| 3.2<br>3.3 | SMI latency53SMI average latency53SMI frequency54Reported execution time62 | 3<br>4 |

| 5.2        | Persistant variables    88      Non-persistant variables    88             | 8      |

| 6.1        | Execution time                                                             | 2      |

## List of Theorems

| 2.1 | Virtual Machine Monitor | <br>26 |

|-----|-------------------------|--------|

|     | vii cuui muchine montor | <br>-0 |

# List of Definitions

| 2.1  | System Executive Software         | 17 |

|------|-----------------------------------|----|

| 2.2  | Code                              | 17 |

| 2.3  | Agent                             | 17 |

| 2.4  | Basic Code                        | 17 |

| 2.5  | Atomic Function                   | 17 |

| 2.6  | Task                              | 17 |

| 2.7  | Set of Tasks                      | 17 |

| 2.8  | Round                             | 17 |

| 2.9  | Payload                           | 18 |

| 2.10 | Set of Payloads                   | 18 |

| 2.11 | Set of Data                       | 18 |

| 2.12 | Memory Unit                       | 18 |

| 2.13 | SMI Handler                       | 18 |

| 2.14 | Set of Registers                  | 18 |

| 2.15 | Resume Instruction                | 18 |

| 2.16 | Set of SMI                        | 18 |

| 2.17 | Maximum Latency                   | 18 |

| 2.18 | Maximum Memory Size               | 18 |

| 2.19 | Set of Requirements               | 18 |

| 2.20 | Set of Threats                    | 18 |

| 2.21 | Set of Assumptions                | 19 |

| 2.22 | Time Elapsed Measurement Function | 19 |

| 2.23 | SMM-Based Security Tool           | 19 |

|      |                                   |    |

## List of Algorithms

| 5.1 | Measure the integrity of hypervisor dynamic data                        | 87  |

|-----|-------------------------------------------------------------------------|-----|

| 5.2 | Manage to call function LoadData()                                      | 91  |

| 5.3 | Load the data to be measured from DRAM to SMRAM                         | 93  |

| 5.4 | Manage to call function ComputeHash( )                                  | 95  |

| 5.5 | Compute data hash                                                       | 97  |

| 5.6 | Manage to call function VerifyHash( )                                   | 99  |

| 5.7 | Verify data hash                                                        | 100 |

| 5.8 | Verify and set registers to reinforce SMM security                      | 101 |

| 5.9 | Verify SMMR interface integrity and trigger a late launch instruction . | 102 |

|     |                                                                         |     |

Chapter 1

### Introduction

Only the paranoid survive.

ANDREW S. GROVE

#### 1.1 Motivation

There are many security issues around computer systems. Thus, it is necessary to enhance security and perform verification tasks to minimize the risk of potential threats become successful attacks. These tasks are usually performed by security tools, such as anti-virus.

In this context some concepts, such as isolation, privilege and view, are fundamental. Security tools must operate isolated to perform their tasks with minimal risk of being hit by the problems they are trying to solve. Security tools need to have high privilege to get in action at the right time and must have a global view of the system, but also good ability to view and deal of its own environment to enhance the chances of success when performing their tasks.

A common security task demanding isolation and high privilege is to measure for checking the integrity of system components, such as the System executive software (operating system or hypervisor). Such verification can be static or dynamic (at run-time).

Generally speaking, to measure the integrity of hypervisors in a static manner, a tool performs a cryptographic service to generate a hash code of the hypervisor static code or data laid out in the main memory. To check the integrity it is necessary and sufficient to generate again the hash code of the same hypervisor static code or data in the memory and compare them. If the hash codes are equal, no changes have happened and then the integrity is preserved. The dynamic measurement is much more complex because the hypervisor dynamic code and data will vary along the hypervisor execution. In both cases, the tool must be deployed in an isolated environment, with enough access privilege whilst preserving the view of the hypervisor code and data.

Then, the problem security analysts are facing is to deploy a security tool in an isolated and high privileged environment, with good view of the system and minimal risk to be tampered with by any threat.

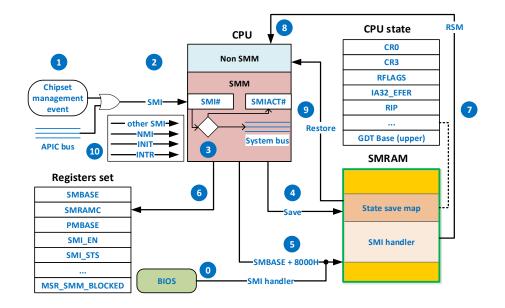

When a System Management Interruption (SMI) is generated the processor enters in the System Management Mode (SMM). So a set of powerful resources, as isolated and protected memory, become available to the SMM executive software (called SMI handler). Those resources can be used by a security tool so it becomes as resourceful as the SMI handler. More details about the SMM resources on Chapter 3.

The System Management Mode (SMM) was introduced in IA-32 architecture into Intel 386SL processor released in 1990, aiming to provide resources to manage the system [87]. Since then, SMM has been a standard architectural feature in IA-64 and IA-32 processors [57]. A key feature of SMM is its high privilege; consequently, the SMM executive software (SMI handler) has higher privileges than the system executive software (operating system or hypervisor), allowing it to manage critical system tasks.

The Intel 386SL processor is mobile version of the Intel 386 processor [66, 71, 87, 97]. Mobile computers have strong requirement for power saving, so they need a robust way to manage power in the system. Thus, SMM was developed to meet such a demand and provide power management and other system management functions, such as hardware control. Prior to SMM, most of these functions were accomplished by In-Circuit Emulation (ICE) tools.

Due to its powerful resources, as: isolated memory, high privilege, high priority and complete view of the system; SMM has been used for purposes other than those described in the Intel manuals [85, 86, 87].

In recent years, SMM was exploited successfully in different ways. For example, by circumventing its protection mechanisms using a technique called "cache poisoning" as described in [45, 148] and by exploiting a fail in implementation in the SMM executive software (SMI handler), which lead to breach the Intel TXT security to exploit the Xen hypervisor, as described in [147]. On the other hand, security researchers have been presenting solutions that capitalise on SMM resources to design and implement new security tools, as HyperSentry [14] to measure the integrity of hypervisors, SICE [15] to provide an isolated execution environment and AppCheck [142] to protect applications by inspecting their code in the physical memory. A discussion about those tools in the context of this work can be seen in 3.4.

Because of this, Intel, OEMs, BIOS and other related manufacturers, have been: 1) extending specifications, such as the addition of a new register to deal with "cache poisoning" attacks [87, 46, 148] (section 3.2.3); 2) changing implementations, such as setting the BIOS to lock the SMM access control register [87, 23, 47] (section 3.2.3 and section 3.5); and 3) introducing new technologies, such as (those technologies, their interrelations and interactions with SMM are discussed at particular sections in chapter 3, as detailed ahead): the Intel Trusted Execution Technology (Intel TXT) [57, 58] (section 2.4.3), the Dual-Monitor Treatment in the Virtual Machine Extensions (VMX) [87] (section 3.3.4) and the Intel Software Guard Extensions (SGX) [111, 60, 10] (section 3.3.5). These changes and their impact on security are discussed later in this thesis, mainly in chapter 3. Observing previous Intel Architecture Software Developers Manual (as[66, 71]) and the chipsets manuals [64, 65, 80, 81], considered in our target chipsets for this research, one can notice that those characteristics and technologies were not or are not present in all machines.

Despite of a considerable number of works capitalising on SMM, there are a lack of research on investigating the SMM itself and its fundamentals. The found works report the use of SMM resources and how they take advantage of some SMM

characteristics, as the use of the SMM isolated memory space (SMRAM), discussed in 3.4. In spite of that, there is a lack of research to understand SMM, establish requirements to use it for security purposes and define an architecture to use SMM as a platform for security tools.

In particular, the SMM-based security tools studied have not been taking full advantage from the SMM resources, as isolation and transparency (the SMI handler executes unnoticed by the system executive software). Also, many of those tools do not abide all the SMM constraints and limits, as latency time. In general, their architectures are modular, being partially deployed in SMM and making connections with their other parts deployed in unprotected areas in the system, which let them subject to general attacks.

Thus, this research investigates the System Management Mode in the context of Intel processors to establish a set of requirements and then design a generic architecture for SMM-based security tools. That generic architecture is tested by building a proof of concept to dynamically measure the integrity of the Xen hypervisor. This measurement is limited to the minimum necessary to prove the concept of the architecture.

#### **1.2 Limits and Scope**

This research limits its scope to Intel processors and chipsets in the x86 platform. We chose Intel due to the amount of open publications, research, attacks and security tools on Intel chipsets and processors available and due to Intel has the biggest market share for processors in the world. However, AMD processors based on the x86 architecture are similar to Intel processors, including the SMM.

We will develop a proof of concept and a manager module for being used in two machines with different chipsets. The reason behind that is because SMM is specific for each machine and the set of resources and registers, SMM or non-SMM, vary depending on the chipset and processor in use at the considered machine. So, any SMM-based tool must be developed specifically for a particular machine. We use Linux as the operating system in all machines utilised in our experiments due to easiness to access PCI bus and the components connected to that bus. In our early experiments we noticed that the Linux distribution CentOS 5.11 is the most appropriated operating system for our work, since that operating system installs Xen hypervisor during its own installation and the tests with a version of our proof of concept using the library libpci was successful in accessing the set of registers we targeted in this work.

The proof of concept aims to perform measurement of essential data of a hypervisor. We choose the Xen hypervisor 4.0 because the amount of open publications and researches available for that hypervisor and because it fits well in the CentOS 5.5 operating system. We focus on **xend-config.sxp** file for the measurement (more details can be found in chapter 6). It is noteworthy that the focus of this work is not to provide a research around measuring the integrity of hypervisors, but capitalising on SMM resources to provide an environment isolated, high privileged and with good view for security tools. In general, the term SMM is used to refer to the set of resources available in the system when the processor is operating in the System Management Mode.

Figure 1.1: **Machine and Chipset 1.** The Acer Aspire X1935, endowed with Intel i5-3450 processor, has the SMRAMC register locked and SMRAM not opened after the bootup process.

The main chipsets considered in this research are (For checking all machines used in this thesis, please check table 3.1):

- Machine and Chipset 1. ACER Aspire X1935, Intel core i5-3450, 3.1GHz, 8GB RAM, Northbridge Ivy Bridge 3rd generation, Southbridge B75, socket Intel LGA 1155. Year of releasing: 2012 [9].

- Machine and Chipset 2. Compac Evo N410c, Intel Pentium III-M, 1.2 GHz, 8GB RAM, Northbridge 82830M, Southbridge ICH3-M. Year of releasing: 2001 [32].

The criteria for choosing those machines was to have one old computer where potentially the SMRAMC register (System Management RAM Control Register see sections and , for more details on this register) is unlocked and SMRAM is opened after the bootup process and another modern computer where potentially the SM-RAMC register is locked and SMRAM is not opened after the bootup process. The SMRAMC register is discussed in details in section 3.2.3.2 and the SMRAM in section 3.2.2.

From the previous paragraph comes our main limitation in this research: to test our proof of concept and met requirements *r*3 (persistent) and *r*4 (cooperative) (the requirements are discussed in 4.4), we need to insert our tool in the the SMM executive software code (called SMI handler), which is available in coreboot [36] (more details about coreboot in section 2.4.1), compile coreboot, record the compilation into a ROM-BIOS chip, install that chip in the target chipset and them test the whole system. However, we do not have all resources for doing these steps in this research. Thus, we assume that our proof of concept is already compiled and embedded in the BIOS, as described in section 4.3. An implication from this limitation is that we just can test our proof of concept in machines which has the SMRAMC register unlocked and SMRAM opened after the bootup process, by copying it from

Figure 1.2: **Machine and Chipset 2.** The HP Compac Evo N410c, endowed with Intel Pentium III processor, has the SMRAMC register unlocked and SMRAM opened after the bootup process.

Figure 1.3: **First set of machines used in the experiments.** This is the first set of machines used in this research (table 3.1).

DRAM to SMRAM. Although this can have implications to requirements r5 (isolated) and r8 (complete) (section 4.4), our assumption also guarantee us to meet requirements r5 and r8, considering the objectives of this thesis.

Figure 1.4: **Second set of Machines used in the experiments.** The second set of machines used in our research (table 3.1).

This research is focusing on the issue of using SMM for security purposes. Attacks or exploits related to SMM are just considered when they are useful for improving the issues related to security.

#### **1.2.1** Scope considering other SMM-Based Security tools

In this section we aim to highlight the main differences, meaning the points not covered for other *SBST* (those one described in table 1.1) and how to make those tools take more advantage from SMM, as by using more SMM resources or by using those resources more intensively.

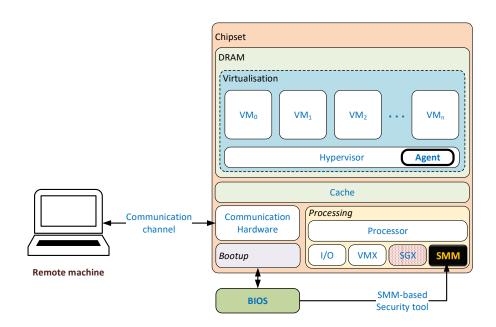

Section 3.4.1 details those tools and presents a brief analysis of them. First, we identify the opportunities for improvement in the tools. For example: HyperCheck [141], HyperSentry [14], auditing tool [61], AppCheck [142], MUSHI [151], SPEC-TRE [149] and IOCheck [150] use a similar architecture, taking in account a remote machine to analyse the collected data and for other management functions (figure 1.5). Although that modularised architecture might address and even overcome issues around the limited amount of SMM memory [87] and time limit constraint of 150  $\mu$ s, which is the maximum amount of time the processor must spend when executing in SMM [90], it opens new ways for attacking the host machine and the tool, as the communication channel (although some tools use attestation mechanisms to prevent that), the drivers and devices used to enable communication and the own remote machine. Moreover, they enlarge the trusted computing base (TCB), since all those items should be in the TCB.

Thus in our proposal all *SBST* components must be deployed in the SMM memory (the SMRAM) to take advantage from the isolation provided by SMM and to minimise the TCB. The *SBST* must execute in the available time according to the algorithms described in chapter 5. Note that, according to chapter 6 our proposal has also a manager module, which does not need to be deployed in the SMM memory or even in the target machine. Since the manager module is used for learning about and researching the target machine, the manager might be used in a machine endowed with the same chipset of the target machine.

Another important issue is that since when entering SMM the processor looks for the first instruction to be executed at the address formed by the content of the SMBASE register + 8000H (by default the SMBASE register content is 30000H, see section 3.2.3.1 for more details) in SMRAM, where the SMM executive software (SMI handler) is located. This implies that any *SBST* must be a modified version of the SMI handler. So, tools use a modified version of the original SMI handler. For example HypeBIOS, SPECTRE and IOCheck use an SMI handler from Coreboot [36], but it is not clear what happens to the original functions of the SMI handler after the modifications have been made, or the level of cooperation between tools and the original SMI handler. So in our proposal we preserve the code and de functions of the original SMI handler, by working cooperatively with it.

To start the SMI handler and consequently the SBST, a System Management Interruption (SMI) must be generated in the chipset. There are common ways to trigger an SMI to start the security tools as writing to the Programmed I/O Port 0xB2H [23, 45]. Because it is a common way to trigger an SMI any attacker might aim to thwart such action by denying the use of that port. Thus, an SBST should take advantage from any SMI generated to start executing its job, which is the simplest way to start and keeping the tool operating. Then our proposal is SMI-independent (requirement r7, the requirements are discussed in 4.4), which means it can start at any SMI.

More details on our proposed architecture can be find in chapters 4, 5 and 6.

| Tool                 | Objective                               | CPU   |

|----------------------|-----------------------------------------|-------|

| HyperCheck [141]     | Check integrity of hypervisors          | Intel |

| HyperSentry [14]     | Check integrity of hypervisors          | Intel |

| HyperGuard [146]     | Check integrity of hypervisors          | *     |

| SICE [15]            | Provide an isolated workload            | AMD   |

| SPECTRE [149]        | Virtual machine introspection           | AMD   |

| IOCheck [150]        | Check integrity of I/O devices          | AMD   |

| Auditing tool [61]   | Auditing cloud computing systems        | *     |

| AppCheck [142]       | Protect integrity of processes          | Intel |

| MUSHI [151]          | Provide isolated environment for VM     | **    |

| hypeBIOS [152]       | Provide isolated environment for VM     | AMD   |

| BIOS Chronomancy[25] | Fix fails in a implementation of a CRTM | Intel |

Table 1.1: **SMM-Based security tools** (*SBST*). This table list the main SMM-Based Security tools considered in this work, providing their objectives and the target platform (as Intel and AMD)

(\*) Not defined in the paper.

(\*\*) Not Implemented. It was only a proposal of framework for AMD platforms.

#### **1.2.2** Scope considering other technologies present in the chipset

Considering our scope of Intel processors, the main technologies which might be present in the chipset and which might have some interaction with an *SBST* are Intel TXT, Intel VMX, Intel SGX, TPM, UEFI. Again note that not all chipsets are endowed with VMX support (see section 3.3.4 for more details) and that SGX technology is not yet available commercially (see section 3.3.5 for more details).

#### 1. INTRODUCTION

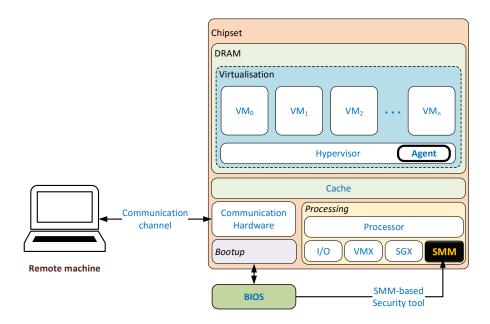

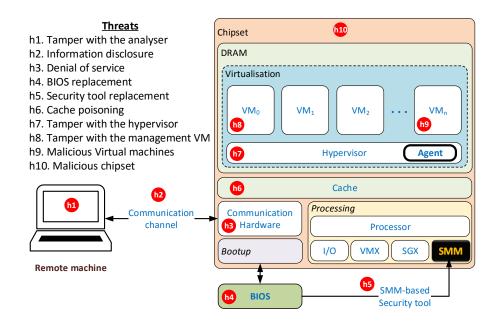

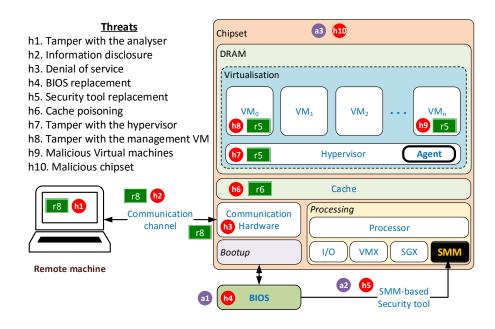

Figure 1.5: **Present** *SBST* **architecture**. This figure presents the current architecture used for most *SBST*s. The figure reflects a comum chipset, where the host machine is using a virtualization layer (section 2.3.2). It is noteworthy that not all chipsets are endowed with VMX support (see section 3.3.4 for more details) and that SGX technology is not yet available commercially (see section 3.3.5 for more details).

We have not identified any issue related to those technologies, which can have impact in our proposal, as making an *SBST* stops working or behaving in an unpredictable way. However, it is noteworthy that: Intel VMX and its interactions with SMM are well defined (see section 3.3.4). Our proposal is based on BIOS, so we do not considerer the interaction of SMM with UEFI, however those interactions are specified in [2] and can be subject of a new research topic as also, TPM and SGX. We do not use TPM in this work, but we believe it can be used to improve our *SBST* as discussed in HyperCheck [141]. SGX is not available yet commercially but there is some documentation available (see section 3.3.5 for details). Intel SGX might be a good answer for low-level security issues since it takes security to the processor level. However, we believe our *SBST* proposal may work cooperatively with SGX. We do not identify any issue related to Intel TXT (see section 2.4.3, on Intel TXT).

#### 1.3 Significance

An intended outcome of this research is to identify and establish a set of requirements, which should be met when developing a SMM-based security tool. Those requirements arise out of the limits and constraints of the SMM. The requirements contributes to harden the SMM-based security tool and make it more likely to be usable in a real environment, by enabling the tool to utilise more resources of SMM. A second intended outcome is to design a generic architecture for a SMM-based security tool in compliance with the requirements. Generic architecture in this context means that the architecture holds for any SMM-based security tool, no matter its security task, provided that the requirements are met. The last intended outcome is to built a proof of concept to test and then demonstrating the validity of the architecture. This proof of concept should consist of a agent module, which is deployed in the SMM memory and implements the security task of the tool; and a manager module to help the tool developer to understand the particularities of a target chipset. The manager module does not need to be deployed in the SMM memory, since it is used to probe and research a target machine and then understand the capabilities and limitations of such a machine. The machine probed is not necessarily the machine where the agent will be deployed, but it needs to have the same or similar chipset.

#### 1.4 **Research Questions**

This section defines a main research question and three specifics questions to guide this work. The subject of this research is how to use the System Management Mode to offer a resourceful environment to a security tool.

#### 1.4.1 Main Research Question

The main research question aims to provide the direction for this work, guiding the research efforts.

**Main question.** *Can we specify a hardened and isolated security tool capitalising on SMM resources, while considering the limits and constraints of those resources?*

The System Management Mode has a set of powerful resources available to its executive software (SMI handler), which can be used to build a hardened and isolated security tool. However, those resources have firm limits, as amount of memory available, and constraints, as maximum latency time. A SMM-based security tool must abide by such limits and constraints. Some security tools capitalising on SMM resources, as HyperSentry [14], HyperCheck [141], auditing tool [61], AppCheck [142], SPECTRE [149] and IOCheck [150] use a modularised architecture, where a security task is divided in subtasks and each module is responsible to perform one subtask. Then, the modules are deployed in different parts of the system and in another machine. A common configuration in this scenario is to have a module in the SMM memory (SMRAM), another one in the DRAM or in a PCI card and another module in a remote machine. The remote machine is normally responsible for analysing the collected data in the target machine. That architecture is designed to deal mainly with the SMM memory limitation and the maximum latency time. Although it is a good approach, it lost the main reasons to use SMM: the strong isolation. Besides, this enlarge the TCB by adding, for example, a PCI card or another machine. In chapter 3 there are details, explanations and schemes about SMM and those tools

#### 1.4.2 Specific Research Questions

To help answering the main questions, we propose three specific research questions. Each question addresses a specific phase of this research and serves as input to the next one. First one deals with the establishment of requirements to harden, isolate and improve a SMM-base tool, while dealing with the limits and constraints of SMM resources. The second question addresses the issue of design a generic architecture to meet the requirements. The last question addresses the feasibility of such a generic architecture.

**Q1.***Can we establish a set of requirements to harden, isolate and improve an SMMbased security tool?*

Security tools can take advantage from SMM resources to harden themselves and enhance the capacity to accomplish their designed task. For example, The SMM memory offers strong isolation to the SMM executive code and data. Also, the SMM executive code has total control and global vision of the system when the processor enters in the SMM. Thus, to understand the limits, constraints, resources, mechanisms and components of SMM, it is required to investigate SMM, its resources and the system components involved in the SMM operation. As this research is considering Intel processors, it is also required to understand the relationship between SMM and other technologies present around Intel processor, such as Intel Trusted Execution Technology (Intel TXT) [57, 58], Intel Virtual Machine Extensions (Intel VMX) [87] and Intel Software Guard Extensions (Intel SGX) [111].

**Q2.***Can we design a generic architecture to fit SMM-based security tools with different tasks, while meeting a set of requirements to harden, isolate and deal with SMM limits and constraints (by generic architecture, we meant one able to fit different security tools with different tasks)?*

Most existent SMM-based security tools, as HyperSentry [14] and HyperCheck [141], employ a modularised architecture comprising of modules deployed in different parts of the system to perform their tasks. Although such an architecture addresses some limitations and constraints of SMM, they leave modules out of the isolation protection of SMM memory. Allegedly, the majority of SMM-based security tools use SMM to achieve strong isolation. So, that modularised architecture does not make much sense. Besides, that architecture enlarges the TCB by adding system components, as PCI cards and remote machines. To take full advantage of SMM resources, a new architecture must be designed. That new designed architecture for SMM-based security tools must deal with all limitations and constraints of SMM and use SMM resources to harden themselves and guarantee the maximum isolation for the whole tool. Also, it need to be generic enough to fit security tools with different tasks.

**Q3.**Can we build a proof of concept to demonstrate the feasibility of a generic architecture, which fits SMM-based security tools, addresses SMM limits and constraints, hardens the fit tool and isolate the whole code and data of the tool?

Build a SMM-based tool is a tricky job, since SMM resources has firm limits and

constraints. For example, the maximum latency time recommend by Intel is 150  $\mu s$ . Above that time there is the risk of system executive software time-outs [90]. Performing any security task in such a time limit is hard. Observe, for instance, table 3.4 with the execution time reported for some SMM-based security tools. There are other challenges, as how to deploy the tool into SMM memory to guarantee isolation, since the SMM memory access is locked when the processor is not in SMM. The access to SMM memory is allowed when the processor is in SMM, but the full control of the system is passed to the SMM executive software. Another challenge is how to start the tool once it is deployed in SMM, since de processor always starts the SMM executive software when entering in SMM. From this, arise out another challenge: the security tool needs to cooperate with the SMM executive software, since the SMM executive software is exclusive user of SMM resources and after the deployment of the security tool both will be in the same memory space and competing for the processor time. Another important issue is the chipset model of the target machine. Each chipset model and sometimes each chipset family (a set of chipset models) may specify SMM in a different ways. Also, any OEM manufacturing chipsets can implement SMM components in different ways too. Thus, a prove of concept should consist of two part: a security agent, to perform the designed security task; and a probe module to investigate the target chipset. Note that the probe module does not need to be deployed into SMM and it can investigate the chipset in any machine, provided that the chipset model is the same in the probed machine and in the target machine.

#### 1.5 Contribution

- 1. A detailed review and description of the SMM resources and components. SMM resources and components have been changing over the years. Some changes were motivated by attacks, as locking the SMRAMC register (System Management RAM Control Register see sections 3.2.3.2 and A.2 after the bootup process. Other changes were motivated by the introduction of different technologies in the processor, as the dual-monitor treatment for SMM in the Intel Virtual Machine Extensions (Intel VMX) [87]. A deep understanding of SMM is essential to use it. So, this research investigate SMM and describe its resources according to Intel definitions. From a practical context, this research investigate SMM in two chipsets, identifying and describing its components. More details can be found in chapter 3.

- 2. Analysis of SMM-based security tools and the opportunities to improve them. This research analyses the implementation and architecture of security tools capitalising on SMM resources and their security tasks, as: HyperCheck [141], to check the integrity of hypervisors; AppCheck [142], to check the integrity of applications; SPECTRE [149], to perform virtual machine introspection; and IOCheck [150], to check integrity of I/O devices. After analysing the tools, this research describes opportunities to improve the security tools. More details in section 3.4.

- 3. Analysis of SMM attacks and how to thwart them. Attackers also have been capitilising on SMM resources by exploiting SMM to attack specific targets,

as the Xen hypervisor in [145], or to have a isolated and resourceful platform to deploy malwares [23, 47]. Thus, this research analyses the main published attacks against SMM and indicates how they can be thwarted. More details in section 3.5.

- 4. Establishment of a set of requirements to use SMM for security purposes. The SMM was created to manage high priority system management tasks. Moreover, Intel recommends in its Software Developer's Manual [87] that SMM should not be used for "General-purposes". Such a recommendation aims to preserve the important SMM functions, since SMM resources have strict limits and constraints and is too risky let a "General-purpose" software violates those limits and constraints and disturb the correct function of SMM components, as by overwriting the SMM executive software SMI Handler (more details in section 3.2.4 and 3.4). However, the fact that the system offers timely and powerful resources when the processor is in SMM is motivating enough to investigate a way to use SMM in the more transparently way possible. So, this research establishes a set of requirements, which a security tool must met to overcome those limits and constraints, allowing the use of SMM for "Security-purpose". More details about the requirements in chapter 4.

- 5. **Design of a generic architecture for SMM-based security tools.** This research designs an architecture generic enough to fit SMM-based security tools with different functions. While there are many works designing tools for specific security purposes, this research focus on providing a architecture to be used for many security tools aiming to accomplish different security tasks. More details in chapter 5.

- 6. A proof of concept to probe chipsets and manage and deploy a SMM-based hypervisor integrity measurement security tool. Although the generic architecture is designed to fit SMM-based security tools with different functions it is neither convenient nor possible to build a proof of concept for all possible security tasks. Then, this research focus in build a proof of concept to one security tasks: measure the integrity of a hypervisor. In the context of this research to measure the integrity of a hypervisor means to define some portions of code or data or both and check the their integrity. So, this research focus on Xen Hypervisor, version 4, performing on CentOS 5.11, to perform measurement of file xend-config.spx. More details can be found in chapter 6

#### 1.6 List of Publications

- 1. Article: William de Souza and Allan Tomlinson. Virtualisation Without a Hypervisor in Cloud Infrastructures: An Initial Analysis - PGNet 2013, Liverpool, UK.

- 2. Article: William de Souza and Allan Tomlinson. Understanding threats in a cloud infrastructure with no hypervisor WorldCIS 2013, London, UK.

- 3. Article:William de Souza and Allan Tomlinson. A Threat Model for a Cloud Infrastructure with no Hypervisor - International Journal of Intelligent Computing Research (IJICR), ISSN 2042 4655, Issues 1/2, Volume 5 (2014), pp. 405-411.

- 4. Article: William de Souza and Allan Tomlinson. SMM Revolutions IEEE Big-DataSecurity 2015, New York, USA.

- 5. Article: William de Souza and Allan Tomlinson. SMM-based hypervisor integrity measurement IEEE CSCloud 2015, New York, USA.

#### 1.7 Overview of the Research

The remain of this work is organised as follow:

Chapter 2 brings the background knowledge of this work, explaining the context and technologies involved in this research and building the definitions necessary to provide the answer to the research questions.

Chapter 3 investigates and details the SMM resources and components in chipsets. It presents related works and SMM-based security tools, analysing opportunities to improve those tools. It also presents the attacks capitalising on SMM and discusses if they are feasible nowadays and ways to thwart such attacks.

From the previous discussions, chapter 4 defines a set of requirements, which should be met for any SMM-based security tool.

Chapter 5 outlines a generic architecture for SMM-based security tools, describing and discussing how the requirements can be meet and the algorithms to implement the solution.

Chapter 6 discusses the implementation and evaluation of the manager module and the agent (the *SBST* itself).

Chapter 7 presents the conclusion of this work and directions for future works in sub-areas of this research.

# Background

Sorry to be a wet blanket. Writing a bitcoin description for general audiences is bloody hard. There's nothing to relate it to.

**"Satoshi Nakamoto"**

# 2.1 Introduction

Chapter 1 introduced the problem around security tools, which need to protect themselves, to have high privileges and good view of the system and of their own environment. In summary: strong isolation, high privilege and good view. Those issues motivated research to use SMM for security purposes. However, capitalising on SMM is a challenging task, considering its limitations, constraints and the components.

The present chapter contextualise the security problem addressed in this research, positioning that problem in the big picture of security in the computational system. The chapter presents a set of definitions required to formulate and design the answers for research questions. It discusses the context of security in an abstract view from the highest level considered in this work, a cloud, to the lowest, SMM and its resources in a machine hosting a virtualised environment, by looking at the security issues on cloud computing and virtualisation and describing the principles behind those technologies. We call this contextual issue as vertical security level. Then, it discusses the environmental issues around the SMM: the components in the host machine competing for processor time, memory space and with concurrent security tasks; by analysing and describing the current state-of-art of technologies as UEFI and Trusted Computing. We call this environmental issue as horizontal security level. Finally, the chapter analysis and discusses works related to the system executive software integrity, as integrity measurement, hardening and new architectures, which are considered when building the proof of concept in chapter 6. Section 3.4 addresses security tools capitalising on SMM.

Figure 2.1 presents a overview of the security problem discussed in this research. The context of the problem is a cloud computing environment, comprising of one or more machines represented in the figure by their chipset. The chipset, as defined in section 2.3.3, is a more useful artefact to be considered in this research than the complete machine. Each chipset hosts in its main memory (DRAM) a virtualised environment comprising of one manager virtual machine ( $VM_0$ ), one or

Figure 2.1: **Security Context.** The security context of this research problem comprises of a vertical security level from the more general concept of a cloud computing, which is more visible for users, to the more specific component the SMM, which is chipset specific; and a horizontal security level considering the bootup process and processing issues and the technologies related to them.

more guest virtual machines ( $VM_1$  to  $VM_n$ ) and a hypervisor. The cache memory takes part of the problem, since some SMM attacks are perpetrated via cache [45]. Then, we have two low-level blocks: bootup, consisting of components and technologies related more to the security issues during bootup process, as BIOS, UEFI, Intel TXT, TPM; and processing, consisting of components and technologies related more to the security issues during the processing tasks. So, the vertical security level puts the research problem in context, relating it to security issues in the: cloud, chipset, memory, virtualisation layer and cache. The horizontal security level considers the research problem in its environment, relating it to security issues in the components of the bootup and processing blocks.

The chapter is organised in four main sections and a discussion and a summary section. The first section presents the set of definitions built to develop the solution for the research problem presented in the chapter 1. Second section addresses the vertical security level around the SMM and third section addresses the horizontal security level around SMM. The fourth section presents the works related the system executive software integrity. After, a discussion and a summary of the work reported in this chapter are presented.

# 2.2 Definitions

This section presents the definitions used when establishing the requirements and designing the generic architecture.

In this work, the term "Technology" is used to designate an implementation of a technique. For example, a hypervisor is a technique for managing virtual machines. Xen [18, 28, 137, 59] is an implementation of a Hypervisor. So, in that example the hypervisor is the technique and Xen is the technology.

Numerical bases are represented by a letter in the rightmost end of each number, as follow: **H for hexadecimal**, **B for binary and D or no letter for decimal**.

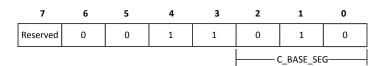

In this work we use the verb "set" to indicate the action in which a register or a bit in a register (a position in the register, as in figure 3.4) have its value changed to "1" and the verb "clear" to indicate the action in which a register or a bit in a register (a position in the register) have its value changed to "0".

# **Definition 2.1 (System Executive Software)**

The system executive software SES is a code artefact with management functions in a computational system. Examples of system executive software are operating system and hypervisors.

# **Definition 2.2 (Code)**

Code is a set of instructions written in any programming language to perform designed actions in a deterministic way.

# **Definition 2.3 (Agent)**

An agent is a code artefact designed to take a preprogrammed action autonomously, whenever it perceives a determined change in its environment.

# **Definition 2.4 (Basic Code)**

A basic code **bc** is a piece of code comprising of basic management functions in a SMMbased security tool. The rationale behind the **bc** is to perform tasks which are independent of the payload loaded into the SMM-based security tool.

# **Definition 2.5 (Atomic Function)**

An atomic function is a set consisting of one or more instructions performed in sequence, without interruption and constrained by a time limit. That time limit must be less than 150  $\mu$ s. An example of atomic function is computing the hash code of a memory region.

# **Definition 2.6 (Task)**

A task  $t_i$  is a well-defined function of a SMM-based security tool, which can be divided into a finite set of subtasks as  $t_i = \{t_{i1}, t_{i2}, ..., t_{nm}\}$ , where each subtask  $t_{ij}$  performs an atomic function. An example of well-defined task is measure the integrity of essential hypervisor data.

#### Definition 2.7 (Set of Tasks)

A set of tasks  $T = t_1, t_2, ..., t_n$  is a set, where each task  $t_i$  performs a well-defined function. It is not possible to say, a priori, that the set of tasks is a finite set.

# **Definition 2.8 (Round)**

A round is the amount of work done by a function related to a task or a sub-task being executed, without crossing the time limit available, which in general is not enough to complete

#### 2. BACKGROUND

a task or a sub-task. A round starts with when an  $smi_i$  is triggered and finishes when a **rsm** instruction is performed.

#### **Definition 2.9 (Payload)**

A payload p is a piece of code embedded into bc to perform a well-defined task. A payload can be thought as a task implementation.

#### **Definition 2.10 (Set of Payloads)**

A set of payloads  $P = \{p_1, p_2, ..., p_n\}$  is a set, where each payload  $p_i$  performs a welldefined task. It is not possible to say, a priori, that the set of payloads is a finite set.

#### Definition 2.11 (Set of Data)

A set of data  $D = \{d_1, d_2, ..., d_n\}$  is a finite set of data to support the execution of a SMM-based security tool.

#### **Definition 2.12 (Memory Unit)**

A memory unit  $mem_{SPACE}[i]$  is a memory space, such as  $mem_{RAM}[i]$ ,  $mem_{SMRAM}[i]$ ,  $mem_{BIOS}[i]$ , where *i* is an index in the memory space, indicating a specific location in that memory space.

#### **Definition 2.13 (SMI Handler)**

The SMI handler SH is the SMM executive software, which is implementation, chipset and OEM dependent.

#### **Definition 2.14 (Set of Registers)**

A set of registers  $REG = \{reg_1, reg_2, ..., reg_n\}$  is a finite set of registers related to SMM.

#### **Definition 2.15 (Resume Instruction)**

*The* resume instruction *rsm is an instruction to signal the processor to exit from SMM.*

#### **Definition 2.16 (Set of SMI)**

A set of SMI  $SMI = \{smi_1, smi_2, ..., smi_n\}$  is a finite set of interrupts to signal the processor to enter SMM, which is implementation, chipset and OEM dependent.

#### **Definition 2.17 (Maximum Latency)**

The maximum latency *ml* is the maximum time a SMM-based security tool can spend when executing in *SMM*.

#### **Definition 2.18 (Maximum Memory Size)**

The maximum memory size *ms* is the maximum memory size a SMM-based security tool can use in  $mem_{SMRAM}[i]$ .

# **Definition 2.19 (Set of Requirements)**

A set of requirements  $R = \{r_1, r_2, ..., r_n\}$  is a finite set of requirements that must be met by a SMM-based security tool.

# **Definition 2.20 (Set of Threats)**

A set of threats  $H = \{h_1, h_2, ..., h_n\}$  is a finite set of threats identified in the current SMM-based security tool architecture.

# **Definition 2.21 (Set of Assumptions)**

A set of assumptions  $A = \{a_1, a_2, ..., a_n\}$  is a finite set of assumptions made to deal with complexity and time constraints due to impossibility or inconvenience to tackle all issues or threats identified in the research work.

# **Definition 2.22 (Time Elapsed Measurement Function)**

The time elapsed measurement function te(f()) is a function to measure the time elapsed of a function f().

# Definition 2.23 (SMM-Based Security Tool)

A SMM-based security tool SBST is defined as  $SBST = \{bc, p_i, t_i, D, mem_{SMRAM}, rsm\}$ . Thus, an SBST has a basic code, responsible for management functions and a payload performing a well-defined security task. SBST has a set of data **D** to support its execution and it should be laid in the SMRAM; the instruction rsm must be used by SBST to finalise its execution.

# 2.3 Context and Technologies

This section explains and contextualises the problem addressed in this research, considering the abstract vertical security level, as showed in figure 2.1. We consider the cloud the highest level because it is a more general concept and more visible to users, whereas the SMM is the lowest level because it is more specific, depending on the chipset, less visible to users and high privileged. As a general rule the lower the component in the vertical security level, the higher the privilege. In the vertical security level, cloud computing is considered the highest entity, comprising of one or more machines, each machine represented for its own chipset. The chipset has many parts, including the virtualisation layer, memories, components of bootup and processing. The virtualisation layer are hosted by the DRAM memory and has the virtual machines in its high level and the hypervisor in low level. Cache memory is positioned in a lower level than DRAM, since it is accessed before the DRAM by the processor, so this is a sort of privilege. Finally, we consider the SMM as the lowest level due to its powerful resources and we also consider that an successful attack to SMM can compromise all the higher components In the vertical security level. The components of bootup block are discussed ahead in the present chapter and the components of processing block are discussed in chapter 3.

# 2.3.1 Cloud Computing

Cloud computing provides an infrastructure for customers to run their applications and store their information. It allows several virtual machines, from different customers, to exist on the same physical machine capitalising on economy of scale, in a dynamic and scalable computational environment at a cost affordable for customers [48, 131]. Although this is the main appeal for a cloud infrastructure it is also the main concern for customers, since the shared environment is prone to threats that can be exploited for a malicious party [30, 38, 63]. For example, a malicious VM can start an attack against the whole infrastructure, targeting components as: another VM running on the same server, the hypervisor or the underlying hardware; and potentially exploiting a wide range of vulnerabilities in the virtualised environment [108, 126].

The importance of cloud computing is more related to the benefits for businesses than its technical aspects. So, the discussion about cloud computing should start in a business environment, where a company needs to decide to keep its own infrastructure or migrate it to the cloud environment [62]. Migrate means to move IT issues and resources to the Cloud Provider, with potential cost reduction, faster time to market, greater market share, innovation and customer loyalty [55].

There are some confusion about the term cloud, specially because the own Internet was referred as a cloud because users access resources through a browser with no idea where such resources are located. To clarify that issue a set of features based on [55, 112, 114, 131] is defined and listed below, so that any pool of resources must have those features to be considered as a cloud computing environment:

- Internet technologies. The pool of resources must be available by means of internet technologies.

- Services-based. The pool of resources is offered as well-defined services, ready to be used by users.

- Scalable and elastic resources. Resources available for any user in the pool must increase or decrease, according to the demands of such a user.

- **Measured use.** The use of resources in the pool, formatted as a services, must be accounted, measured and billed to clearly express their utilisation by any user.

- **Shared resources.** The resources in the pool are used by one user or shared by two or more users, transparently, allowing economy of scale.

- **Fault tolerant.** The resources in the pool must be fault tolerant in such a way that whenever a failure occurs, the resources of users must be migrated from failed resources to working resources, transparently for users.

- **Security.** The pool of resources must be protected against internal and external threats, including the protection and isolation among users.

Once a pool of resources can be recognised as cloud computing and considering the Services-based features, a cloud computing provider can adopter three service models, as described below [55, 112, 131]:

- **Software-as-a-Service (SaaS).** This model has a rich variety of services and offers software as service in the cloud environment. Some examples are: the Google app suite, offering a wide range of application, the Salesforce, offering an applications to manage the sales process and customer relationship, and Symantec, offering security services as anti-virus and firewall from the cloud. Some variations of SaaS are Application-as-a-Service, Security-as-a-Service (as McAfee [7]), Information-as-a-Service and Management-as-a-Service [55].

- Platform-as-a-Service (PaaS). In this service model, the cloud provider offers a platform of hardware (network, processor, storage and so on) and software (operating system, compilers, libraries and so on), so the users can deploy

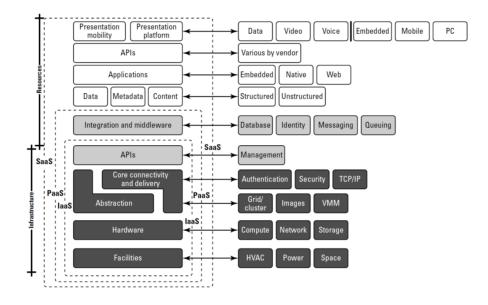

Figure 2.2: The Cloud Reference Model (figure from [131]). An abstract view of the cloud computing environment layers.

or migrate their applications to the cloud computing environment without worry about the amount of resources necessary in the moment of migration or in the future. Examples of such service model are: the Microsoft Azure [34], Red Hat [6] and Engine Yard [55].

• Infrastructure-as-a-Service (IaaS). This service model offers infrastructure to specific needs of users, as storage, processing power and communication capabilities, so that the user has control over those resources to a certain extent. Amazon Web Services is an example of this model [1]. Some variations of IaaS are Storage-as-a-Service, Database-as-a-Service, Network-as-a-Service and Computer-as-a-Service [55].

Figure 2.2 depicts an abstract view of the cloud computing environment layers, considering the concepts discussed before. This abstract view is also know as The Cloud Reference Model [131].

One last taxonomy is important about cloud computing. It is related to the deployment model, as listed below from the more restrict to the more embracing [55, 112, 131]:

- **Private cloud.** This model refers to a cloud computing environment built to serve a particular organisation. It can be built on or off premises and can be managed or operated by the organisation or a third party.