# Platform Verification and Secure Program Execution in Embedded Devices

Mehari Gebrehaweriya Msgna

Thesis submitted to the University of London for the degree of Doctor of Philosophy

> Information Security Group Department of Mathematics Royal Holloway, University of London

> > 2015

# Declaration

This doctoral study was conducted under the supervision of Dr. Konstantinos Markantonakis.

The work presented in this thesis is the result of original research carried out by myself whilst enrolled in the Department of Mathematics as a candidate for the degree of Doctor of Philosophy. This work has not been submitted for any other degree or award in any other university or educational establishment.

Signature ...... Mehari Gebrehaweriya Msgna Date:

## Publications

- Mehari Msgna, Raja Naeem Akram, Konstantinos Markantonakis and Keith Mayes, "Subscriber Centric Conditional Access System for Pay-TV Systems", in IEEE 10th International Conference on e-Business Engineering (ICEBE), pages 450-455. Coventry, United Kingdom: IEEE Computer Society, September 11-13, 2013.

- Mehari Msgna and Colin Walter, "An Overview of PIC Microcontrollers and Their Suitability for Cryptographic Algorithms", *chapter* in Secure Smart Embedded Devices, Platforms and Applications. Konstantinos Markantonakis and Keith Mayes (*Eds*). Springer, 2013.

- Mehari Msgna, Konstantinos Markantonakis and Keith Mayes, "The B-Side of Side Channel Leakage: Control Flow Security in Embedded Systems", in The 9th International Conference on Security and Privacy in Communication Networks (SecureComm), series LNICST. Tanveer Zia, Albert Zomaya, Vijay Varadharajan and Morley Mao (Eds.), volume 127. Sydney, Australia: Springer, September 2013.

- Mehari Msgna, Konstantinos Markantonakis, David Naccache and Keith Mayes, "Verifying Software Integrity in Embedded Systems: A Side Channel Approach", in The 5th International Workshop on Constructive Side-Channel Analysis and Secure Design (COSADE), series LNCS. Emmanuel Prouff (Eds.), volume 8622. Paris, France: Springer, April 2014.

- Mehari Msgna, Konstantinos Markantonakis and Keith Mayes, "Precise Instruction-Level Side Channel Profiling of Embedded Processors", in The 10th International Conference Information Security Practice and Experience (ISPEC), series LNCS. Xinyi Huang and Jianying Zhou (Eds.), volume 8434. Fuzhou, China: Springer, May 2014.

- Konstantinos Markantonakis, Raja Akram and Mehari Msgna, "Secure and Trusted Application Execution on Embedded Devices" in The 8th International Conference on Security for Information Technology and Communications (SECITC'15), *series* LNCS. David Naccache and Emil Simion (*Eds.*). Bucharest, Romania: Springer, June 2015.

## Acknowledgement

This thesis would not have been possible without the support of a number of people.

My initial and foremost thanks goes to my family. Especially, Samrawit Abegaz for being so patience throughout my study. I would also like to thank my supervisor Dr. Konstantinos Markantonakis and Prof. Keith Mayes for all their support and guidance.

I would like to offer my gratitude to Sheila Cobourne for her wonderful reviews of this thesis. During my stay in Royal Holloway, University of London I have met many people who inspired me in so many ways, I would like to convey my thanks to all of you.

## Abstract

Recently, hardware manufacturers are increasingly outsourcing their production process into countries with lower cost structure. Although this reduces the cost of hardware production, it also creates opportunity for attackers to hack into the supply chain and change the original design of the hardware components. Such changes could range from short circuiting a module (for instance random number generators) to inserting parasite circuits and new masks (such as hardware Trojan circuits). These kind of intrusions are difficult to detect through pure functional testing. Furthermore, attacks on runtime program attributes (eg. fault injection attacks) are increasing in number and sophistication.

In this thesis we propose techniques for platform verification and secure program execution that can be used in low-end to medium-end embedded systems. Our design incorporates a pre-deployment device verification and dedicated security module that monitors the program's properties during execution. Both our predeployment and runtime verification methods constitute compile and execution time computations to reduce the time required for security checks during runtime.

In the core of this thesis, we analyse the current threats to the embedded systems platform and programs. This leads to two major contributions spanning the pre and post integration of embedded systems into the larger electronic equipment. We propose side channel based pre-deployment platform verification techniques. In our techniques we use instruction and basic block level side channel templates to identify anomalies within the target platform. Our approach does not require prior detailed knowledge of the inner workings of the program or the platform under test. Furthermore, we also propose the design of a generic runtime secure program execution architecture. Our proposal protects the target program's runtime data, instructions and control flow jumps during its execution. To achieve this goal without affecting the performance of the main processor we introduce a dedicated hardware module. Finally, we provide the test implementations of our proposals along with their performance measures.

# Contents

| 1 | Intr          | roduction 17                                                                                                                                |  |  |  |  |

|---|---------------|---------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|   | 1.1           | Setting the Scene                                                                                                                           |  |  |  |  |

|   | 1.2           | The Evolution of Embedded Systems                                                                                                           |  |  |  |  |

|   | 1.3           | Motivation and Challenges                                                                                                                   |  |  |  |  |

|   | 1.4           | $Contributions \dots \dots$           |  |  |  |  |

|   | 1.5           | Thesis Structure    26                                                                                                                      |  |  |  |  |

| 2 | $\mathbf{Em}$ | edded Systems Architecture 29                                                                                                               |  |  |  |  |

|   | 2.1           | Introduction $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $30$                                                            |  |  |  |  |

|   | 2.2           | Embedded Systems Architectures                                                                                                              |  |  |  |  |

|   |               | 2.2.1 Microprocessor Unit $\ldots \ldots \ldots \ldots \ldots \ldots \ldots 32$                                                             |  |  |  |  |

|   |               | $2.2.2  \text{Memory}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                     |  |  |  |  |

|   |               | 2.2.3 Input/Output $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 35$                                               |  |  |  |  |

|   |               | $2.2.4  Bus \ldots 35$                                         |  |  |  |  |

|   |               | 2.2.5 Supporting Devices $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 36$                                                |  |  |  |  |

|   | 2.3           | Characteristics of Embedded Processors                                                                                                      |  |  |  |  |

|   |               | 2.3.1 Design Parameters                                                                                                                     |  |  |  |  |

|   |               | 2.3.2 Classification $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 37$                                                    |  |  |  |  |

|   | 2.4           | Application Development Tools                                                                                                               |  |  |  |  |

|   |               | 2.4.1 Source Code Editor $\ldots \ldots 40$                                  |  |  |  |  |

|   |               | $2.4.2  \text{Compiler} \dots \dots$  |  |  |  |  |

|   |               | $2.4.3  \text{Debugger}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                   |  |  |  |  |

|   |               | $2.4.4  \text{Simulator}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                  |  |  |  |  |

|   |               | 2.4.5 Device Programmer $\dots \dots \dots$ |  |  |  |  |

|   | 2.5           | Example Applications                                                                                                                        |  |  |  |  |

|   | 2.6           | Summary                                                                                                                                     |  |  |  |  |

| 3 | Atta | acks on Embedded Systems                                 | 45 |

|---|------|----------------------------------------------------------|----|

|   | 3.1  | Introduction                                             | 46 |

|   | 3.2  | Invasive Attacks                                         | 47 |

|   |      | 3.2.1 Delayering                                         | 47 |

|   |      | 3.2.2 Block Localisation                                 | 48 |

|   |      | 3.2.3 Microprobing $\ldots$                              | 50 |

|   |      | 3.2.4 Circuit Extraction                                 | 50 |

|   |      | 3.2.5 Circuit Modification                               | 51 |

|   | 3.3  | Semi-Invasive Attacks                                    | 52 |

|   |      | 3.3.1 Local Heating                                      | 52 |

|   |      | 3.3.2 Ultraviolet Attacks                                | 53 |

|   |      | 3.3.3 Optical Emission Analysis                          | 53 |

|   | 3.4  | Non-Invasive Attacks                                     | 54 |

|   |      | 3.4.1 Side Channel Analysis                              | 54 |

|   |      | 3.4.2 Data Remanence                                     | 56 |

|   |      | 3.4.3 Fault Injection                                    | 56 |

|   | 3.5  | Summary                                                  | 57 |

| 4 | Secu | urity In Embedded Systems                                | 58 |

|   | 4.1  | Introduction                                             | 59 |

|   | 4.2  | Code Hardening                                           | 60 |

|   | 4.3  | Side Channel Protection                                  | 62 |

|   | 4.4  | Tamper Resistance                                        | 62 |

|   | 4.5  | Redundant Execution                                      | 64 |

|   | 4.6  | Trusted Platform Module (TPM)                            | 65 |

|   | 4.7  | ARM's TrustZone                                          | 66 |

|   | 4.8  | GlobalPlatform                                           | 67 |

|   |      | 4.8.1 Application Management                             | 68 |

|   |      | 4.8.2 Trusted Execution Environment                      | 68 |

|   | 4.9  | Remaining Security Challenges                            | 69 |

|   |      | 4.9.1 Post-production Pre-deployment Device Verification | 70 |

|   |      | 4.9.2 Runtime Secure Execution                           | 71 |

|   | 4.10 | Summary                                                  | 72 |

| Ι        | Po  | ost-pr  | oduction Pre-deployment Measures                   | 74  |

|----------|-----|---------|----------------------------------------------------|-----|

| <b>5</b> | Cor | ntrol F | low Verification                                   | 75  |

|          | 5.1 | Introd  | luction                                            | 76  |

|          | 5.2 | Devic   | e Modelling                                        | 78  |

|          |     | 5.2.1   | Model Parameters                                   | 79  |

|          |     | 5.2.2   | Principal Components Analysis (PCA)                | 82  |

|          |     | 5.2.3   | Fisher's Linear Discriminant Analysis (F-LDA)      | 83  |

|          | 5.3 | Contr   | ol Flow Reconstruction                             | 84  |

|          | 5.4 | Contr   | ol Flow Verification                               | 85  |

|          | 5.5 | Imple   | mentation and Results                              | 86  |

|          |     | 5.5.1   | Model Parameters                                   | 87  |

|          |     | 5.5.2   | Calculating The Most Probable State Sequence       | 90  |

|          |     | 5.5.3   | Verifying The Reconstructed State Sequence         | 91  |

|          | 5.6 | Summ    | nary                                               | 91  |

| 6        | Sof | tware   | Integrity Verification                             | 93  |

|          | 6.1 | Introd  | luction                                            | 94  |

|          | 6.2 | Instru  | ction-Level Template Construction                  | 95  |

|          | 6.3 | Dimer   | nsionality Reduction                               | 97  |

|          |     | 6.3.1   | Sum of Difference of Means                         | 97  |

|          |     | 6.3.2   | Means-Variance                                     | 97  |

|          |     | 6.3.3   | Means-PCA                                          | 98  |

|          | 6.4 | Instru  | ction Classification                               | 98  |

|          |     | 6.4.1   | Multivariate Gaussian Probability Density Function | 99  |

|          |     | 6.4.2   | k-Nearest Neighbors Algorithm                      | 99  |

|          | 6.5 | RSA S   | Signature Screening Algorithm                      | 100 |

|          | 6.6 | Basic   | Block Integrity Verification                       | 101 |

|          | 6.7 | Imple   | mentation and Results                              | 104 |

|          |     | 6.7.1   | Instruction-Level Template Construction            | 105 |

|          |     | 6.7.2   | Dimensionality Reduction                           | 107 |

|          |     | 6.7.3   | Instruction Classification                         | 109 |

|          |     | 6.7.4   | Basic Block Integrity Verification                 | 113 |

|          | 6.8 | Summ    | nary                                               | 115 |

| Π                          | R     | Runtime Secure Execution                                 | 117 |  |  |

|----------------------------|-------|----------------------------------------------------------|-----|--|--|

| 7 Program Data Security 11 |       |                                                          |     |  |  |

|                            | 7.1   | Introduction                                             | 119 |  |  |

|                            | 7.2   | Related Work                                             | 121 |  |  |

|                            | 7.3   | Attack Model                                             | 122 |  |  |

|                            | 7.4   | Dual-Stack Architecture                                  | 123 |  |  |

|                            |       | 7.4.1 TwinStack: Redundant Stack Operations              | 124 |  |  |

|                            |       | 7.4.2 IntegrityStack: Verifying Integrity of Stack Items | 125 |  |  |

|                            | 7.5   | Implementation and Analysis                              | 127 |  |  |

|                            |       | 7.5.1 Implementation                                     | 127 |  |  |

|                            |       | 7.5.2 Performance Overhead                               | 130 |  |  |

|                            |       | 7.5.3 Latency                                            | 131 |  |  |

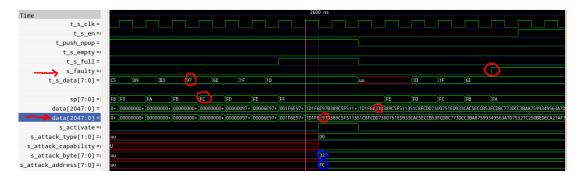

|                            |       | 7.5.4 Attack Detection Capability Evaluation             | 132 |  |  |

|                            | 7.6   | Summary                                                  | 132 |  |  |

| 8                          | Pro   | ogram Instructions and Control Flow Security             | 135 |  |  |

|                            | 8.1   | Introduction                                             | 136 |  |  |

|                            | 8.2   | Basic Blocks                                             | 138 |  |  |

|                            | 8.3   | Control Flow                                             | 139 |  |  |

|                            |       | 8.3.1 Inter-Procedural Control Flow                      | 139 |  |  |

|                            |       | 8.3.2 Intra-Procedural Control Flow                      | 142 |  |  |

|                            | 8.4   | Instructions Integrity                                   | 144 |  |  |

|                            | 8.5   | Implementation                                           | 147 |  |  |

|                            |       | 8.5.1 Lookup Tables                                      | 147 |  |  |

|                            |       | 8.5.2 Hash Computation                                   | 149 |  |  |

|                            | 8.6   | Summary                                                  | 150 |  |  |

| 9                          | Coi   | nclusion and Future Work                                 | 152 |  |  |

|                            | 9.1   | Summary and Conclusions                                  | 153 |  |  |

|                            | 9.2   | Recommendation for Future Research                       |     |  |  |

| Bi                         | iblio | graphy                                                   | 156 |  |  |

| $\mathbf{A}$               | Sele  | ected AVR Instructions                                   | 181 |  |  |

# List of Figures

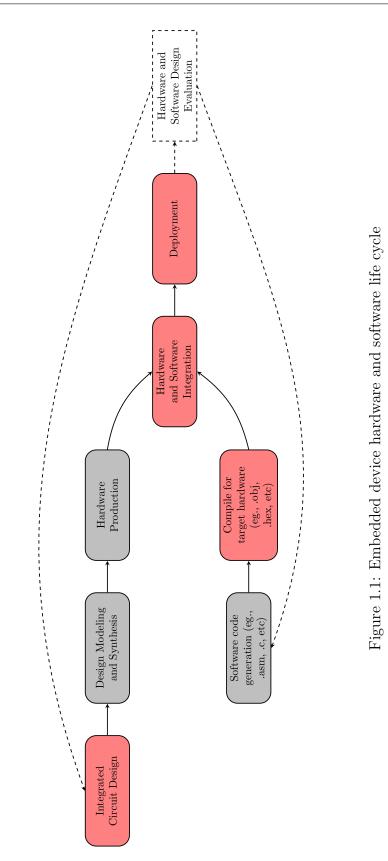

| 1.1 | Embedded device hardware and software life cycle                                                        | 24 |

|-----|---------------------------------------------------------------------------------------------------------|----|

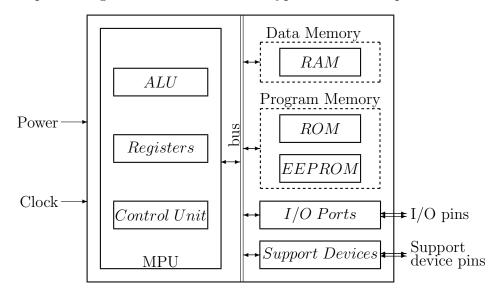

| 2.1 | General architecture of embedded processor                                                              | 32 |

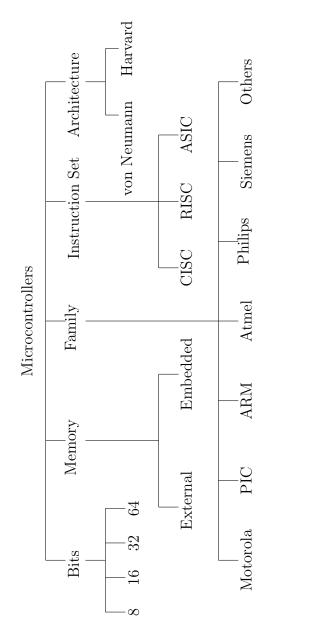

| 2.2 | Classification criteria of microcontrollers                                                             | 39 |

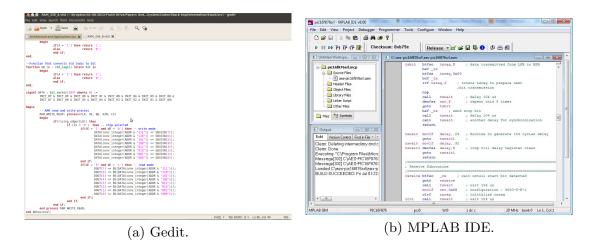

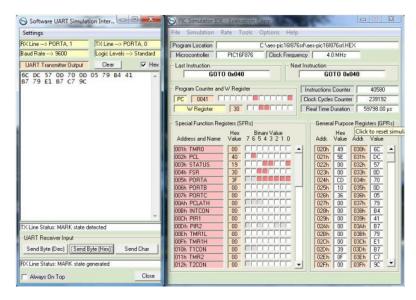

| 2.3 | Example of source code editor software                                                                  | 41 |

| 2.4 | PIC simulator IDE, a software designed to simulate a range of PIC                                       |    |

|     | microcontrollers.                                                                                       | 42 |

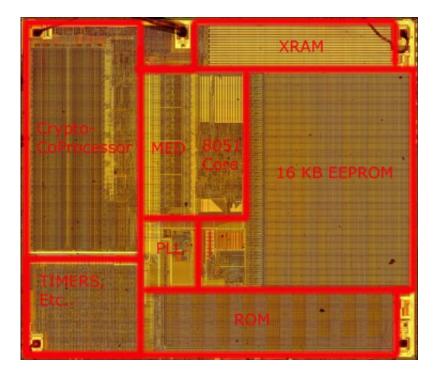

| 3.1 | Different blocks of a decapsulated Infineon SLE66 [1]                                                   | 49 |

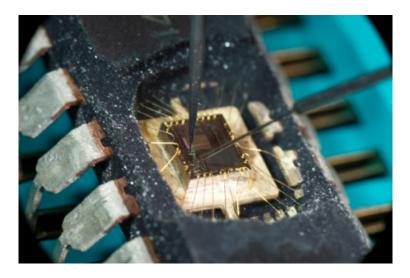

| 3.2 | Probing needles on a decapsulated semiconductor chip [2]. $\ldots$                                      | 50 |

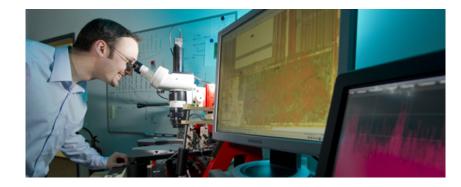

| 3.3 | Taking microscopic pictures of the inner circuitry of a semiconduc-                                     |    |

|     | tor chip [2]. $\ldots$ | 51 |

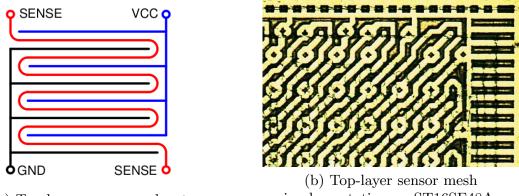

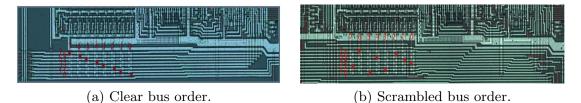

| 4.1 | A top layer sensor mesh setup and practical implementation $[3].$                                       | 63 |

| 4.2 | A clear and scrambled bus lines [4]                                                                     | 63 |

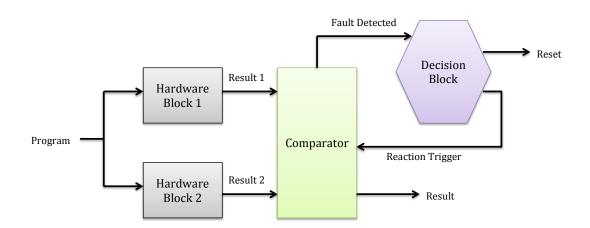

| 4.3 | A simple hardware redundant execution setup                                                             | 64 |

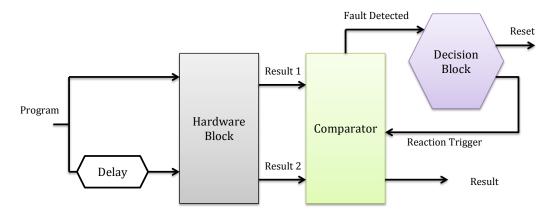

| 4.4 | A simple time redundant execution setup                                                                 | 65 |

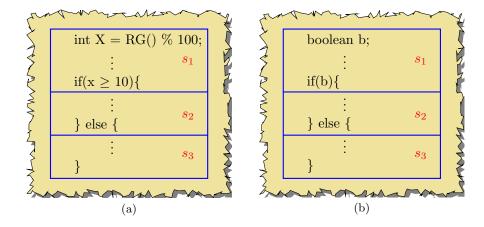

| 4.5 | Generic architectural view of ARM TrustZone                                                             | 67 |

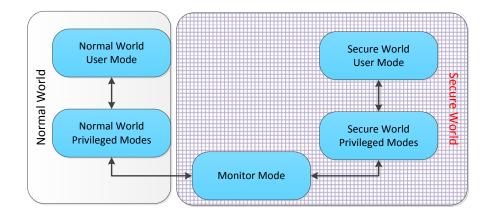

| 5.1 | A Hidden Markov Model representation of a device executing a                                            |    |

|     | program with five states (A, B, C, D and E). The power consump-                                         |    |

|     | tion is the observable output that reveals partial information about $% \mathcal{A}$                    |    |

|     | the executed states                                                                                     | 79 |

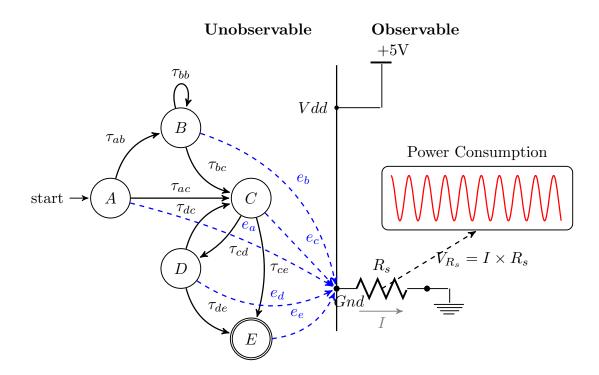

| 5.2 | Integer and boolean branching statements in code segment with $3$                                       |    |

|     | states                                                                                                  | 81 |

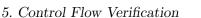

| 5.3 | Test program's control flow diagram.                                                                    | 87 |

| 5.4 | High-level description of the test program                                                              | 87 |

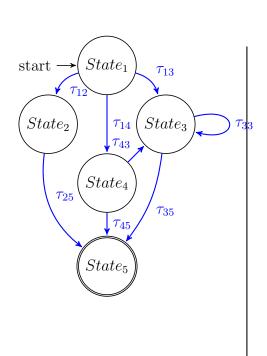

| 5.5  | Mean of the power traces of the states illustrated in Fig. 5.3                                  | 89  |

|------|-------------------------------------------------------------------------------------------------|-----|

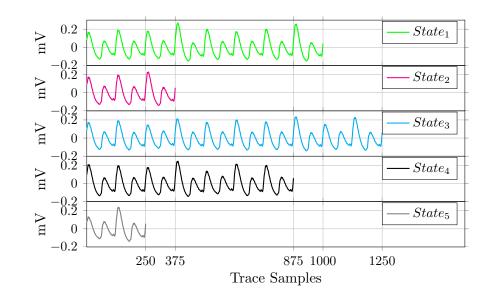

| 5.6  | Original data after PCA                                                                         | 89  |

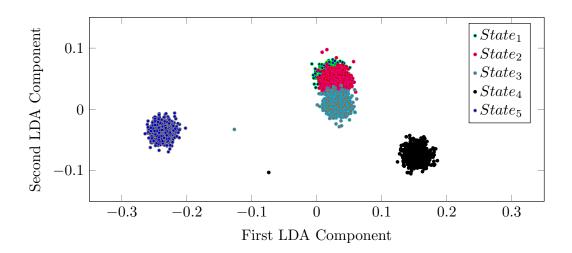

| 5.7  | Original data after F-LDA                                                                       | 90  |

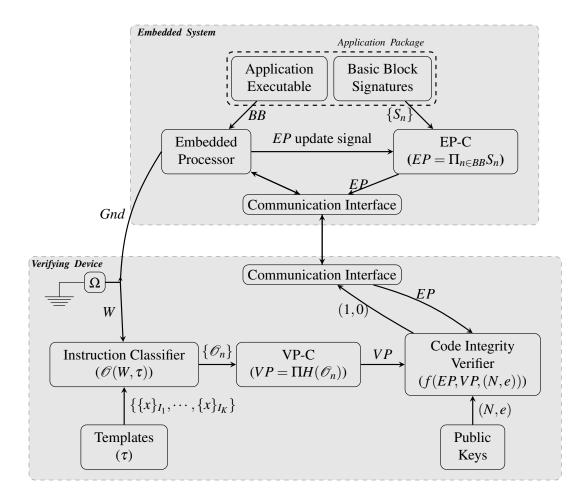

| 6.1  | Basic block integrity verification block diagram                                                | 102 |

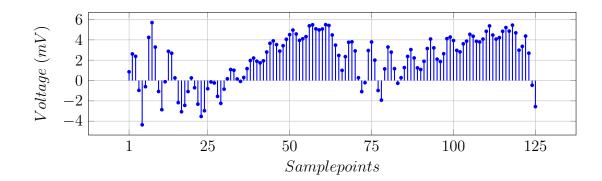

| 6.2  | Power consumption waveform of selected ATMega163's one clock                                    |     |

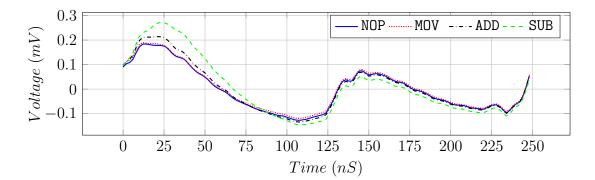

|      | cycle instructions (NOP, MOV, ADD and SUB)                                                      | 106 |

| 6.3  | Power consumption waveform of selected ATMega163's two clock                                    |     |

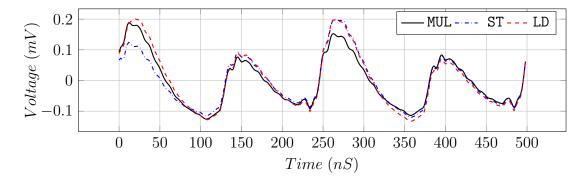

|      | cycle instructions (MUL, ST and LD)                                                             | 107 |

| 6.4  | Sum of difference of means.                                                                     | 108 |

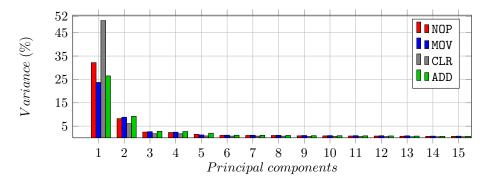

| 6.5  | Overall variance of the original data accounted for the first 15                                |     |

|      | principal components of the instructions NOP, MOV, CLR and ADD. $% \mathcal{A} = \mathcal{A}$ . | 108 |

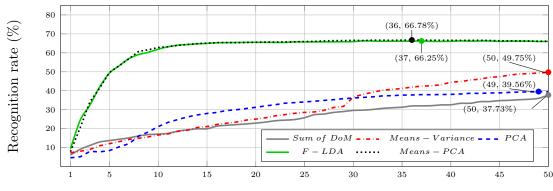

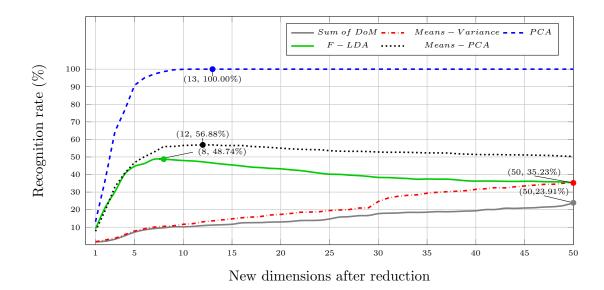

| 6.6  | Classification rate after dimensionality reduction using <i>Multivari</i> -                     |     |

|      | ate Gaussian Probability Density Function for all 39 instructions.                              | 110 |

| 6.7  |                                                                                                 | 112 |

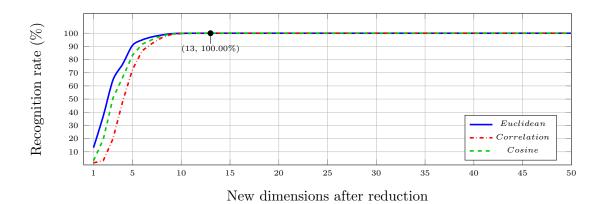

| 6.8  | Instruction recognition rate for all 39 instructions using $K$ -Nearest                         |     |

|      | Neighbors Algorithm for $k=1$ after applying the dimensionality re-                             |     |

|      | duction techniques                                                                              | 113 |

| 6.9  | Recognition rate for all 39 instructions using $K$ -Nearest Neighbours                          |     |

|      | Algorithm with different distance functions for k=1 after applying                              |     |

|      | PCA                                                                                             | 114 |

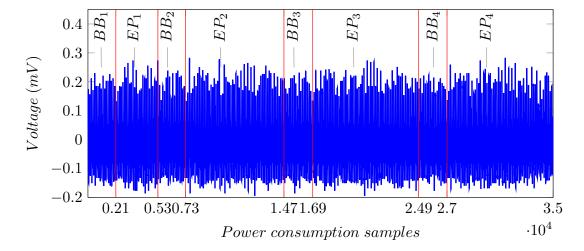

| 6.10 | Power consumption of the processor when executing PIN checking                                  |     |

|      | application with embedded processor parameter update in between                                 |     |

|      | the basic blocks                                                                                | 114 |

| 7.1  | Fault Injection: Attack example on stack items                                                  | 120 |

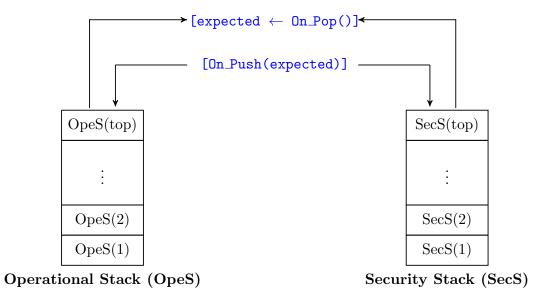

| 7.2  | Double stack architecture                                                                       | 124 |

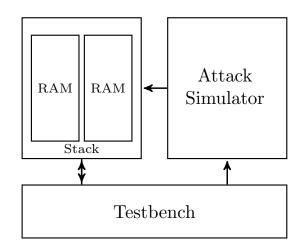

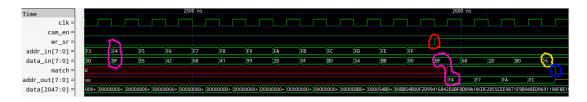

| 7.3  | Hardware implementation of dual-stack and attack simulator                                      | 128 |

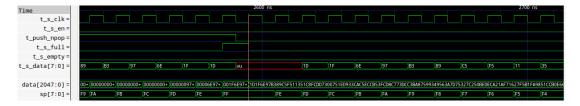

| 7.4  | Normal single stack VHDL implementation                                                         | 128 |

| 7.5  | TwinStack VHDL implementation                                                                   | 129 |

| 8.1  | Assembly code segment and its basic blocks                                                      | 138 |

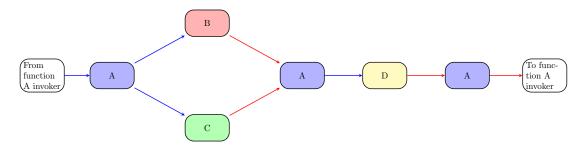

| 8.2  | Control flow diagram of function A                                                              | 140 |

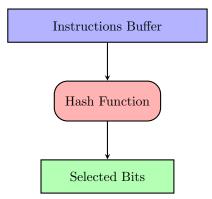

| 8.3  | Hash generating scheme                                                                          | 146 |

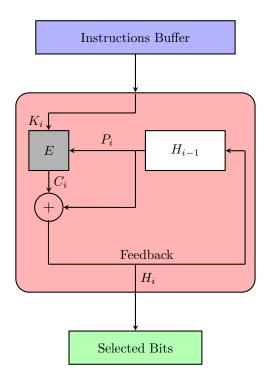

| 8.4  | Davies-Meyer hash generation scheme.                                                            | 147 |

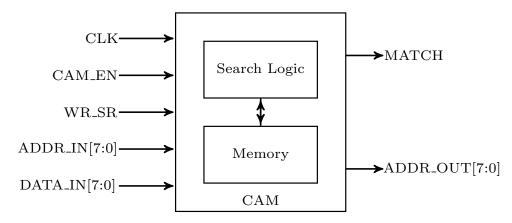

| 8.5 | Content Addressable Memory (CAM) architecture. | 148 |

|-----|------------------------------------------------|-----|

| 8.6 | 256 byte Content Addressable Memory (CAM)      | 149 |

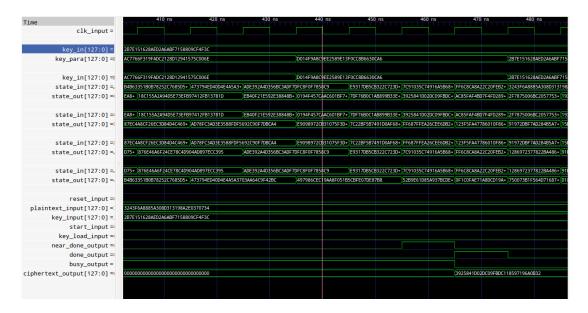

| 8.7 | AES implementation in VHDL                     | 150 |

# List of Tables

| 2.1        | CISC, RISC and equivalent Pseudo- Code for Multiplying two<br>Memory Contents                                                                                                                               |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.2        | A list of embedded system applications                                                                                                                                                                      |

| 5.1        | Transition probability distribution of the program illustrated in<br>Figure 5.3. The columns represent next states and the rows rep-<br>resent current states                                               |

| 6.1        | Percentage of true ( <b>bold</b> ) and false positive recognition rate for<br>a selected instructions using MVGPDF. The rows and columns<br>represent executed and recognised instructions respectively 109 |

| 6.2        | Percentage of true ( <b>bold</b> ) and false positive recognition rate for a selected instructions using kNN. The rows and columns represent                                                                |

|            | executed and recognised instructions respectively                                                                                                                                                           |

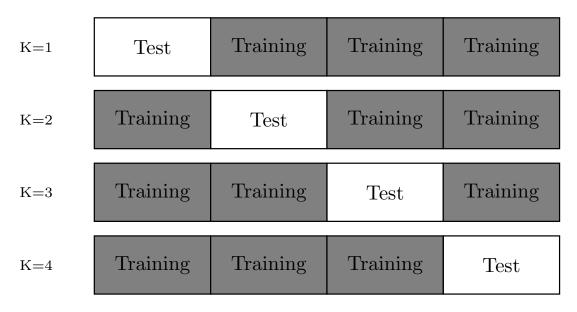

| 6.3        | Average percentage of true ( <b>bold</b> ) and false positive recognition<br>rate for a selected instructions using kNN in k-fold cross validation. 111                                                     |

| 7.1        | Number of additional instructions introduced by the countermeasure 131                                                                                                                                      |

| 7.2        | Overall increase in executed instructions of software implementa-                                                                                                                                           |

| 7 9        | tion of the countermeasure                                                                                                                                                                                  |

| 7.3<br>7.4 | Latency measurements of the countermeasures                                                                                                                                                                 |

|            | lated works                                                                                                                                                                                                 |

| 8.1        | Function property lookup table $TABLE_{property}$                                                                                                                                                           |

| 8.2        | Function property lookup table $TABLE_{property}$ for example function. 141                                                                                                                                 |

| 8.3        | Basic block information lookup table $(TABLE_{BasicBlock})$ 143                                                                                                                                             |

| 8.4 | Basic block information lookup table for function | n i | В |   | • | • | • | • | • | 144 |

|-----|---------------------------------------------------|-----|---|---|---|---|---|---|---|-----|

| A.1 | AVR's instructions seleted for our experiments.   |     |   | • |   | • |   |   |   | 183 |

# List of Abbreviations

| ADC  | Analogue to Digital Converter                 |

|------|-----------------------------------------------|

| AES  | Advanced Encryption Standard                  |

| AIK  | Attestation Identity Key                      |

| ALU  | Arithmetic Logic Unit                         |

| APDU | Application Protocol Data Unit                |

| ASIC | Application Specific Instruction Set Computer |

| ATM  | Automated Teller Machine                      |

| AU   | Arithmetic Unit                               |

| CA   | Certificate Authority                         |

| CAM  | Content Addressable Memory                    |

| CFG  | Control Flow Graph                            |

| CISC | Complex Instruction Set Computer              |

| CM   | Control Module                                |

| CPU  | Central Processing Unit                       |

| CRT  | Chinese Remainder Theorem                     |

| CSE  | Common Subexpression Elimination              |

| CT   | Computerized Tomography                       |

| CU   | Control Unit                                  |

| DAC  | Digital to Analogue Converter                 |

| DES  | Data Encryption Standard                      |

| DFA  | Differential Fault Analysis                   |

| DPA  | Differential Power Analysis                   |

| DVD  | Digital Versatile Disc                        |

| ECG  | Electrocardiogram                             |

| ECU  | Electronic Control Unit                       |

| EEG  | Electroencephalography                        |

|      |                                               |

| EEPROM | Electrically Erasable Programmable Read Only Memory     |

|--------|---------------------------------------------------------|

| EFP    | Environmental Failure Protection                        |

| EFT    | Environmental Failure Testing                           |

| EK     | Endorsement Keys                                        |

| EMG    | Electromyography                                        |

| FCG    | Function Call Graph                                     |

| FIFO   | First In First Out                                      |

| F-LDA  | Fisher-Linear Discriminant Analysis                     |

| FIPS   | Federal Information Processing Standard                 |

| GSM    | Global System for Mobile                                |

| HMM    | Hidden Markov Model                                     |

| IC     | Integrated Circuit                                      |

| IDE    | Integrated Development Environment                      |

| IO     | Input/Output                                            |

| IR     | Instruction Register                                    |

| ISS    | Instruction Set Simulator                               |

| JCVM   | Java Card Virtual Machine                               |

| kNN    | k-Nearest Neighbours                                    |

| LU     | Logic Unit                                              |

| LM     | Lunar Module                                            |

| MAR    | Memory Address Register                                 |

| MDR    | Memory Data Register                                    |

| MISR   | Multiple Input Shift Register                           |

| MPU    | Microprocessor Unit                                     |

| MRI    | Magnetic Resonance Imaging                              |

| MVGPDF | Multivariate Gaussian Probability Distribution Function |

| NFC    | Near Field Communication                                |

| OCR    | Optical Character Recognition                           |

| OS     | Operating System                                        |

| PC     | Personal Computer                                       |

| PCA    | Principal Components Analysis                           |

| PCR    | Platform Configuration Register                         |

| PDA    | Personal Digital Assistant                              |

| PIN    | Personal Identification Number                          |

|        |                                                         |

| RAM                 | Random-Access Memory                |

|---------------------|-------------------------------------|

| RISC                | Reduced Instruction Set Computer    |

| ROM                 | Read Only Memory                    |

| RSA                 | Rivest Shamir Adleman               |

| SEM                 | Scanning Electron Microscope        |

| SHA                 | Secure Hash Algorithm               |

| SPA                 | Simple Power Analysis               |

| $\operatorname{SR}$ | Status Register                     |

| SRAM                | Static Random-Access Memory         |

| SRK                 | Storage Root Key                    |

| TEE                 | Trusted Execution Environment       |

| TEM                 | Transmission Electron Microscope    |

| TPA                 | Template Power Analysis             |

| TPM                 | Trusted Power Module                |

| TV                  | Television                          |

| UV                  | Ultraviolet                         |

| VHDL                | VHSIC Hardware Description Language |

| VHSIC               | Very High Speed Integrated Circuit  |

|                     |                                     |

## Chapter 1

# Introduction

#### Contents

| 1.1 | Setting the Scene                 | 18        |

|-----|-----------------------------------|-----------|

| 1.2 | The Evolution of Embedded Systems | 18        |

| 1.3 | Motivation and Challenges         | <b>22</b> |

| 1.4 | Contributions                     | 23        |

| 1.5 | Thesis Structure                  | <b>26</b> |

In this chapter, we provide a brief discussion on the evolution of embedded systems. We then deliberate on the motivation and challenges of the thesis. This is followed by the contributions of the thesis to the knowledge on security of embedded systems and program execution. Finally, the chapter concludes by outlining the structure of the thesis with a short description of all subsequent chapters.

### 1.1 Setting the Scene

We start the discussion of this chapter with the history of how embedded systems technology has evolved over the years since its inception. We then explain our motivations for pursuing this research topic and all the challenges that this involves. We also point out our rationale for implementing our security countermeasure techniques. This is followed by a brief discussion of the contributions of this thesis. Finally, we finish the chapter by outlining the structure for the rest of thesis.

### **1.2** The Evolution of Embedded Systems

An embedded system is a complex computing machine made up of multiple modules, where each module can be considered a separate invention. In 1936 Zuse, a German civil engineer, designed the first relay computer, also known as Z1 Computer [5]. The Z1 Computer and consecutive computer designs of the 1940's were dedicated for a single task. These computers had instructions made to accomplish a specific task that the computer was made to be used. Each computer had a different binary-code program called a machine language that told it how to operate [6]. Another feature of early computing systems was that they were too large to be considered "embedded".

In 1947 an important invention occurred, "*The Transistor*" [7]. A transistor is not a computer but has greatly influenced the evolution of a computing system. In 1958 Jack Kilby and Robert Noyce presented their work at a conference in Washington, DC about a solid block of electronic equipment without connecting wires. This became to be known as the first Integrated Circuit (IC) or chip [8]. Over time the concept of re-programmable computing systems was developed from a combination of computing technology, solid state device and traditional electromechanical sequence. This led to the emergence of sophisticated but smaller ICs, such as embedded systems. One of the very first modern embedded systems was the Apollo Guidance Computer designed by Charles Stark Draper [9]. The Apollo Guidance Computer provided computation and electrical interface for guidance, navigation and control of the spacecraft and it was installed on each of the Apollo Control Module (CM) and Lunar Module (LM). It had 16 bit word with 15 bits of data and one parity bit. It also made use of both erasable and permanent memory blocks. The erasable memory block was used to store intermediate results of communication, such as the location of spacecraft, while the program data that did not need changing was stored on the permanent memory.

In 1961 Boeing<sup>1</sup> released the Minuteman I missile. Inside the missile was the Autonetics D-17 guidance computer system [10]. The D-17 was a small serialbinary computer designed for general purposes [11]. When the Minuteman II missile went into mass-production in 1966, the D-17 was replaced with a newer embedded system design, making it the first high-volume production and use of embedded integrated circuit.

After these early and isolated embedded system applications, their price came down, permitting their use in commercial products. In 1969 Nippon Calculating machines approached Intel for the design of 12 custom chips for its new 141-PF printing calculator. However, Intel's engineers suggested a set of four chips called the MCS-4<sup>2</sup>. The MCS-4 contained 4 chips which were the Central Processing Unit (CPU) - the Intel 4004 -, Read-only memory (ROM), random access memory (RAM) and a shift register chip for IO purposes. Intel then launched the Intel 4004 with an advertisement in the November 15, 1971 issue of the Electronic News titled "Announcing the new era in integrated electronics" [12]. That made the Intel 4004 the first general purpose microprocessor that someone can buy from the market and customise it to perform their desired operation.

Since then the size of microprocessors decreased while the number of transistors and computing power increased significantly. In 1965 Gordon Moore in his pa-

<sup>&</sup>lt;sup>1</sup>Boeing is one of the largest and leading aerospace companies and manufacturer of commercial jet liners, defence, space and security systems.

<sup>&</sup>lt;sup>2</sup>MCS-4 is a chip-set designed by Intel in the early 1970s. It contained the 4001 ROM, 4002 RAM, 4003 Shift Register and 4004 processor.

per [13], predicted that the number of transistors per integrated circuit will be doubled roughly every year and will continue to do so for at least a decade. The Intel 4004 was the size of a fingernail but delivered the same computing power as the 1940's computer designs [14] which filled an entire room. Intel 4004 had 2,300 transistors and a circuit line width of 10,000 nanometers. By 2010 an Intelcore processor holds 560 million transistors with a circuit line width between 32 and 45 nanometers. This trend of transistor miniaturisation led to integration of additional functionalities into the chip without having to increase the size of the device, leading to the emergence of the first microcontroller MCS-48 in 1976 [15].

The emergence of the first microcontroller, followed by the continuous increase in sophistication and decrease in size of integrated circuits fuelled the next breakthrough in the evolution of embedded systems. This time it came from Germany and France, not from America. The French Postes, Télégraphes et Téléphones (PTT) deployed integrated circuits embedded in a plastic card as telephone cards [16]. The Germans telephone companies soon followed. These deployments provided a testing ground for embedded systems in a new application area, which was later exported to other industries, as chip based cards provided increased reliability and security.

The early versions of these cards were limited storage capacity memory cards based on a simple fixed logic circuit. However, later in the 1990's microprocessor cards start to emerge onto the scene. These cards can store information as well as dynamically process the stored information without relying on a fixed logic circuit. The German post office conducted the first trials of microprocessor cards for their analogue mobile telephone network. Their purpose was to authenticate users when they join the network to avoid the cloning of mobile phones. The success story of these trials resulted in the deployment of such cards in the GSM<sup>3</sup> network. At the time, telecommunication companies all over the world were rapidly adopting microprocessor cards as telephone cards. However, the banks of the time did not embrace the microprocessor cards quickly.

The development of microprocessor cards coincided with another breakthrough

<sup>&</sup>lt;sup>3</sup>Global System for Mobile Communication (GSM) is a standard for mobile telecommunication industry that is developed and promoted by the GSM Association (GSMA)

in the field of system security and mathematics. The study of cryptography was just emerging from government and military secrecies to the public. The security offered by sophisticated cryptographic algorithms coupled with an improved hardware design paved the way for microprocessor cards to be used as a security tokens. This gave microprocessor cards the edge as a secured token over other technologies. Shortly afterwards the banks followed the footprints of Telecom companies in deploying microprocessor cards as bank cards.

The development of such cards was further facilitated in 1996 when engineers from an IT technology provider (Schlumberger in Austin, Texas, United States of America) designed a microprocessor card that can support a subset of the Java<sup>4</sup> programming language [17]. Such cards are also known as Java Card<sup>5</sup>. This gave birth to the more sophisticated multi-application microprocessor cards, which support the existence and execution of multiple applications from different providers, such as the latest Java Card 3.0 [18] and MULTOS [19]. According to [20], 9 billion Java Cards were deployed since 1998, making it the most widely used embedded system in the world.

The proliferation of such cards into many other applications (for example, the electronic identity cards, passports and driving license) coupled with the advancements in microelectronics helped embedded systems to become one of the most widely deployed computing system. This is even further strengthened by the technological progress in smartphones and the emergence of new technologies (such as the NFC [21] and the Internet of Things [22]). By 2017 two billion NFC enabled devices are predicted to be shipped [23]. Nearly three billion low-end (4, 8 and 16 bit) processors are sold every year [24]. According to [25] a person uses 250 chips or one billion transistors each day. This data was published in 2008 and it is a truism that these numbers will only increase with time.

$<sup>^4\</sup>mathrm{A}$  general purpose programming language designed to create programs capable of running on any computer.

<sup>&</sup>lt;sup>5</sup>Java Card is a multiplication microprocessor card platform which supports subset of the Java programming language and is promoted by the JavaCard Forum.

### **1.3** Motivation and Challenges

A wide range of computing devices are being introduced into our modern life style, performing different tasks, for example, alarm clocks, smartphones, smart watches but also more security critical devices such as bank cards and physical access control systems. With the advancement of the Internet and Internet based services, such devices are increasing in number and sophistication. Furthermore, they are increasingly involved in collecting and processing big amount of data that is paramount for our security. For instance, cyber-physical systems that are used in traffic monitoring and controlling systems.

The security and privacy concerns of users are increasing with the increasing number of different devices through which users access associated services and information. To curve these concerns, several techniques have been proposed to provide hardware-based privacy and security protection. These proposals differ in operation and capability from one system (or device) to another. In other words, a proposed technique's security and privacy architecture becomes specific to the target device. For instance, the difference between the Trusted Platform Module (TPM) [26] and Mobile Trusted Module (MTM) [27] is that they target two different computing systems; a general-purpose computing device and a mobile phone respectively. Other similar solutions are ARMs TrustZone [28] and GlobalPlatform Trusted Execution Environment (TEE) [29].

Having a wide range of security protection options is good but it also means that service providers and system manufacturers, that require security and privacy, have to implement and support a wide range of technologies. In addition, over time several devices have evolved from the original purposes that they were designed for. For instance, initially mobile phones were first designed for voice and later text communications. Similarly, televisions were designed for news and drama but now they are also used to access the Internet. This means in addition to their traditional services they now need to implement internet security techniques as well and the same goes to a number of other devices. The diversity in protection methods creates a complex issue of implementating, integrating, using and managing, not only for the service providers but also the consumers. A possible solution to the aforementioned challenges is to have a unified hardwarebased security and privacy architecture that can be used across different computing platforms (e.g. smart cards, mobile phones, televisions and other embedded devices). We divide the security of embedded systems into two phases; postproduction pre-deployment verification and runtime secure execution. The principle is that the underlying device's processor will have the same hardware-based security architecture that can be used to securely execute all applications regardless of their nature. For example, service providers can offer their services on mobile phones, tablets and televisions without a major design change.

#### **1.4 Contributions**

In this thesis we set out to analyse the security of embedded systems. We start this by looking into the life cycle of an embedded device. Figure 1.1 shows the different stages of an embedded device during its life cycle. An embedded system contains a hardware and software components. Normally, both components have to go through a number of stages before they can be integrated. The design, synthesis and production stages of the hardware component refer to the premanufacturing phases of the integrated circuit. Similarly, the code generation and compilation are the code writing and transformation of the software respectively.

After reviewing the current security threats and countermeasures deployed in embedded devices, we consider modifications to a number of stages within the life cycle of an embedded device. The modified stages are highlighted in red in Figure 1.1. The modifications are spread over different stages of an embedded device's life cycle, from designing the integrated circuit to post-deployment program execution. The questions of how these stages should be modified are the focus of this thesis. Contributions of this thesis extend from chapter 5 to chapter 8.

The main contributions of this thesis are divided into pre-deployment and postdeployment stages. From here on we refer to the pre-deployment and postdeployment changes as platform verification and secure program execution. The pre-deployment platform verification is concerned with identifying undesirable

24

platforms or platform components that can not be detected by only *purely func*tional<sup>6</sup> tests. Such threats include counterfeits and hardware Trojans. The runtime secure program execution is tasked with ensuring the programs are executed securely during runtime.

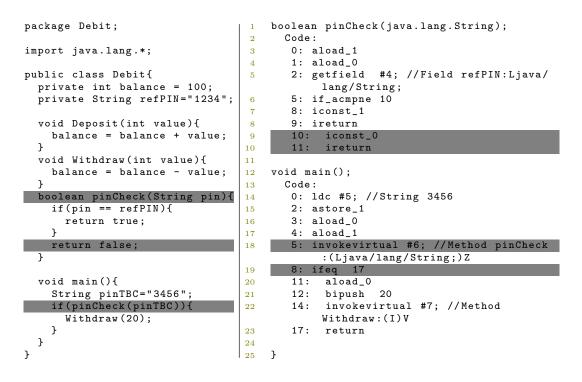

Counterfeits and hardware Trojans are designed to be difficult to detect with purely functional tests. Thus we propose side channel based techniques to verify the hardware and software platforms. First we propose a power consumption based pre-deployment program control flow verification. Then we propose basic block instructions integrity verification. This involves the creation of instruction and basic block level template creation. In addition, it also requires precise template recognition methods. The principle behind this technique is, the user creates instruction and basic block level side channel templates using a few legitimate devices. Later, using these templates he/she verifies the integrity of other devices before they are assembled into the final product. The result of these works are published in international conferences and the papers can be accessed in [30, 31]. In addition, we improved the previously known highest instruction based side channel template matching success, 70.1% [32] on PIC microcontrollers [33], to 100%. Details of this work in available at [34].

The above proposal is to verify a device before it is integrated into the final product. The second part of this thesis is protecting the programs against threats that may come once the product is operational. This deals with program control flow, integrity of executed instructions and runtime program data. To that effect we propose a number of changes to the traditional design of embedded devices. We propose an integrated watchdog module as part of the process design. This watchdog takes additional information generated by a compiler and uses it to ensure the security of the control flow jumps and executed instructions at runtime. To protect the runtime data we propose a dual stack processor architecture, where the second stack is used to ensure the integrity of items in the main stack. We also proposed a dedicated hardware subsystem to verify the control flow and instructions integrity. The module takes input from a compiler generated program attribute and the main processor. Details of these proposals are discussed in the

$<sup>^{6}\</sup>mathrm{A}$  test designed to verify the conformance between a device and its specification.

second part of this thesis. Details of these proposals and their implementations is presented in Chapters 7 and 8.

### 1.5 Thesis Structure

The rest of the thesis is organised as follows:

In chapter 2 we begin the discussion with a brief description of embedded systems. With the ever-changing characteristics of embedded systems discussion on the basic architecture of embedded devices is needed. Therefore, in this chapter we define embedded systems. We then explain the underlying architecture and the different components that it comprises. Following that we discuss the design characteristics and application development process of embedded systems. Finally, we present a list of practical examples.

Attacks on embedded systems are increasing in number and sophistication. These attacks are generally divided into three main categories; invasive, semi-invasive and non-invasive attacks. Invasive attacks physically modify the target device irrecoverably. These changes range from removing the insulation layer of an IC, reverse engineering to reconfiguring the underlying circuit. Non-invasive attacks only require exposure to the surface of the target device but do not disrupt the device's normal operations. Semi-invasive attacks are in between invasive and non-invasive attacks. In chapter 3 we discuss these attacks in detail and provide a number of examples for each category.

Due to the recent increasing in number and sophistication of attacks in embedded systems several countermeasures have been proposed. The countermeasures range from modifying the source code, using dedicated external devices to re-designing the processor architecture. In chapter 4 some of the most commonly utilised countermeasures are discussed. Among them are code hardening techniques, Trusted Platform Module (TPM), ARM's TrustZone, redundant execution and GlobalPlatform's application management and trusted execution environment. We provide explanation and examples of such countermeasures before concluding the chapter by highlighting the remaining security threats to embedded systems.

As with any manufacturing plants, integrated circuit manufacturers are increasingly moving their foundry to countries with a cheaper cost structure. This means electronic equipment makers have to buy their components from all over the world. Therefore, verifying the integrity of such components before they are assembled is paramount for the security of the final product. The first part of our research, *Part I: Post-production Pre-deployment Measures*, deals with this challenge. We present our findings of this challenge in chapters 5 and 6.

One of the pre-installed program's attributes that a product manufacturer may be interested in verifying is the program's control flow paths. The easiest way to do that would be for the component maker to supply the source code and pre-computed valid paths. However, due to intellectual property issues this does not happen often. Therefore, in our work, chapter 5,we use side channel leakage of the device as an alternative information. We use the side channel information to reconstruct the control flow path followed by the processor in executing the target program. We then verify it by comparing it with the pre-computed valid paths. This way the verifier does not need to have a prior knowledge of the inner workings of the program and the component maker does not need to handover sensitive company information.

Another attribute of a program that needs verifying is the integrity of executed instructions. For the same reason as above we selected the side channel leakage of the embedded device to verify the instructions. Chapter 6 presents our work in this area. Our procedure involves building side channel template of the instructions and classification algorithm to recognise executed instructions from the device's leakage. Besides verifying the integrity of instructions this method can also help identify changes to the device's original design such as hardware Trojan as it will be reflected on the side channel leakage.

The second part of our research, *Part II: Runtime Secure Execution*, deals with the challenges of securely executing embedded programs. In this part of our work we proposed techniques that will protect runtime data, control flow and

instructions of a program during execution. Our proposals for runtime secure execution are presented in chapters 7 and 8.

Runtime data is an important attribute of a program security during execution. It is often targeted by an adversary to divert the program's control flow, circumvent countermeasures, extract secret information or simply corrupt the execution result. Such attacks usually involve manipulating items that are pushed/popped into/from the stack. Several countermeasure have been proposed to stop or detect manipulating stack items. In chapter 7, we provide a detail discussion of a stack architecture, operations and countermeasures proposed previously. In addition, we propose an alternative countermeasure that can be used to protect runtime program data on embedded systems. We also provide details of our implementation analysis, computational overhead and detection capability of our proposal.

In chapter 8 we discuss runtime threats to embedded systems control flow and instructions. We provide brief explanation of related works before we discuss our proposals. We then discuss about our control flow verification covering inter- and intra-functional execution flow branches. Furthermore, we propose instruction integrity verification for executed instructions. Our proposals depend on having a dedicated hardware subsystem. It also requires a modified compiler module to extract program attributes during compilation. Finally, we discuss and present implementation results.

Finally, in chapter 9 we conclude the thesis by summarising the contributions and suggesting the future direction of this research. In the appendix section we present additional materials and all source codes of our implementations are available at a public repository [35].

## Chapter 2

## **Embedded Systems Architecture**

#### Contents

| <b>2.1</b> | Introduction                           | 30 |

|------------|----------------------------------------|----|

| 2.2        | Embedded Systems Architectures         | 32 |

| <b>2.3</b> | Characteristics of Embedded Processors | 36 |

| <b>2.4</b> | Application Development Tools          | 40 |

| <b>2.5</b> | Example Applications                   | 43 |

| 2.6        | Summary                                | 44 |

In this chapter, we briefly introduce the main architectural design of embedded systems. This is followed by a discussion on their main characteristics. Then we elaborate on the application development process and tools for embedded systems. Finally, we summarise the chapter by listing the main talking points after a short discussion on the some common embedded system applications.

### 2.1 Introduction

An embedded system is an applied computer system with a dedicated function within a larger mechanical or electrical system often with real-time constraints. That distinguishes them from Personal Computers (PCs) and supercomputers. However, the definition of "embedded system" is fluid and difficult to pin down, as it constantly evolves due to advances in technology and decreases in the cost of implementing various hardware and software components. In recent years, embedded systems have outgrown many of their traditional descriptions. To better understand them it is important to know what these descriptions are and why they may not be accurate today. The most common descriptions of embedded systems are:

- Embedded systems are more limited in hardware and/or software functionality than a personal computer (PC). This holds true for a significant subset of the embedded systems family of computer systems. In terms of hardware limitations, this can mean limitations in processing performance, power consumption, memory, hardware functionality, and so forth. In software, this typically means limitations relative to a PC including fewer applications, scaled-down applications, no operating system (OS) or a limited OS, or less abstraction-level code. However, this definition is only partially true today as circuit boards and software typically found in PCs are being repackaged into more complex embedded system designs.

- An embedded system is designed to perform a dedicated function. Most embedded devices are primarily designed for one specific function. However, we now see devices such as personal data assistant (PDA)/cell phone hybrids, which are embedded systems designed to do a variety of primary functions. Also, the latest digital TVs include interactive applications that perform a wide variety of general functions unrelated to the "TV" function but just as important, such as e-mail, web browsing, and games.

- An embedded system is a computer system with higher quality and reliability requirements than other types of computer systems. Some families

of embedded devices have a very high threshold of quality and reliability requirements. For example, if a car's engine controller crashes while driving on a busy freeway or a critical medical device malfunctions during surgery, serious problems may occur. However, there are also embedded devices, such as TVs, games, and cell phones, in which a malfunction is an inconvenience but not usually a life-threatening situation.

Some devices that are called embedded systems, such as PDAs or web pads, are not really embedded systems. There is some discussion as to whether or not computer systems that meet some, but not all of the traditional embedded system definitions are actually embedded systems or something else. Some feel that the designation of these more complex designs, such as PDAs, as embedded systems is driven by non-technical marketing and sales professionals, rather than engineers. Whether or not the traditional embedded definitions should continue to evolve, or a new field of computer systems be designated to include these more complex systems will ultimately be determined by the industries and research organisations. For now, since there is no new industry-supported field of computer systems designated for designs that fall in between the traditional embedded system and the general-purpose PC systems, this thesis supports the traditional definition of embedded systems. That is a resource constrained integrated circuit designed to perform a limited functionality (usually for a dedicated task) with limited power supply under a harsh environment.

In Section 2.2 we discuss the generic architecture of an embedded processor and its different components. Following in Section 2.3 we elaborate on embedded system characteristics. We explore the design parameters and their classification. In Section 2.4 we explain the process and tools required to develop a program for an embedded device. We continue in, Section 2.5, with a discussion on some common embedded system application areas. Finally in Section 2.6 we summarise the main points of the chapter.

### 2.2 Embedded Systems Architectures

At the centre of an embedded system there is always a processor that controls its activities. This processor has multiple modules, including the Microprocessor Unit (MPU), data and program memory, Input/Output module, bus and other supporting modules depending on the application of the embedded system [36]. Fig 2.1 depicts the general architecture of a typical embedded processor.

Figure 2.1: General architecture of embedded processor

The processor is powered up by supplying a voltage source through the power pin. The clock is a timing signal which is used to synchronise the processor's various components while they execute arithmetic and logic operations or transfer data between different locations. The clock signal can be generated either inside the processor's integrated circuit or obtained externally via the clock input pin. We now discuss the different components of an embedded processor.

#### 2.2.1 Microprocessor Unit

The *Microprocessor Unit* (MPU) is the main module of an embedded processor. It is responsible for the execution of embedded programs that are installed inside the processor. It performs all logic and arithmetic operations and also controls the processor's status. To help it accomplish these activities it has three components: the *Arithmetic Logic Unit* (ALU), *Registers* and the *Control Unit* (CU).

The ALU carries the arithmetic and logic operations required on the operands <sup>1</sup> in the program's instructions. In some processors, the ALU is divided into Arithmetic Unit (AU) and Logic Unit (LU). In such configuration the AU performs the arithmetic operations and the LU deals with the logic operations. In addition, some processors contain multiple AUs, for instance one for fixed-point <sup>2</sup> and another for a floating-point <sup>3</sup> operations. Normally, an ALU has a direct input and output access to the control unit, Random-Access Memory (RAM) (described in detail in Section 2.2.2), and input/output modules (described in detail in Section 2.2.3).

Registers are memory cells that are located inside the MPU. They are used for quick reading, storing and manipulating of data. However, there are also designated registers for special purposes. Some of the special registers that are paramount for executing programs are; the Instruction Register (IR), Memory Data Register (MDR), Memory Address Register (MAR), Program Counter (PC), Accumulator and Status Register (SR). The IR hold the instruction that is currently being executed. The MDR (also known as memory buffer register or data buffer register) holds data that is fetched from the memory. The MAR carries the address of a memory cell that needs to be fetched next. The PC holds the address of the next instruction that needs to be executed. Normally, its value is sequentially incremented unless an instruction is executed that changes it (such as function call instructions and conditional or unconditional branching instructions). The accumulator is a register which holds the intermediate result of an arithmetic or logic operations before the final result is moved to the destination memory location or another register. The status register, is used to save or indicate the status of the MPU. It has a number of bits that can be used to flag exceptions, indicate the arithmetic status of the ALU and the reset status of the MPU.

$<sup>^{1}</sup>$ A data on which the operation (specified by the opcode) is to be performed.

<sup>&</sup>lt;sup>2</sup>A fixed-point is the representation of a number with fixed number of digits after the decimal point.

$<sup>^{3}</sup>$ A floating-point is a number with no fixed number of digits before and after the decimal point. In other words, the decimal point can float.

The final component of the MPU is the Control Unit, which provides timing and control signals for all other components of the embedded processor. Basically the control unit tells the embedded device's memory, ALU, I/O modules and other components how to respond to each instruction executed by the processor.

#### 2.2.2 Memory

In general there are two memory types in embedded processors: *volatile* and *non-volatile*. A volatile memory is a storage where all previous data are generally lost within at most a second or so when the power is turned off. Such storage is also known as a Random Access Memory (RAM), mainly because any location within it can be accessed directly and randomly, rather than sequentially from some starting point, at approximately the same time and its contents can be changed multiple times. On the other hand, non-volatile memory retains its data even when the power source is removed. Examples of such memory are Read-Only Memory (ROM) and Electrically Erasable Programmable Read-Only Memory (EEPROM). Information can only be written into ROM once and cannot be modified again. However, contents of an EEPROM can be erased and reprogrammed repeatedly by applying a higher electrical voltage through the provided program pin of the processor.

In Fig. 2.1, these memory types are classified under two categories; the Data Memory and the Program Memory. The Program Memory is where the application/program is stored. On the other hand, Data Memory is where the processor stores data and variables during runtime. Runtime variables are created during and deleted at the end of the program execution and are normally stored in RAM. However, actual program instructions are required to persist even after the power is removed and therefore are usually stored in ROM and EEPROM. Different processors have different configuration of the Data Memory and Program Memory. For instance the Data Memory and Program Memory of Harvard processors are organised into two separate blocks: the *program memory* and the *data memory* [37]. They are on physically separate buses so that instructions cannot be used as data or *vice versa*. In von Neumann architecture processors the MPU uses a single main memory to store both program instructions and data, and are accessed by through a single bus. Details of Harvard and von Neumann architectures are discussed in Section 2.3. Modern high performance microcontrollers incorporate aspects of both Harvard and von Neumann architectures. The on-chip cache memory is divided into an *instruction cache* and a *data cache* which store copies of values that are used frequently by the MPU. The MPU uses Harvard architecture when accessing the cache.

#### 2.2.3 Input/Output

An input/output is a communication between an MPU and the outside world, possibly human beings or another embedded device. The input/output device (module) assists the MPU in achieving the above task. The input/output data can be can be analogue signal or binary information. The input is the signal or data received by MPU from the outside world and the input device can be, for instance, a keyboard, mouse or other sensors. The output is signal or data sent by the MPU to the outside world and the output device can be a printer, display monitor or a server.

#### 2.2.4 Bus

The bus is a communication channel that data between different components inside the processor is transferred through. Generally an embedded processor has three different buses; address bus, data bus and control bus. The address bus connects the MPU with the memory and carries the address of a location in the memory. This address is then used to identify a specific location and before performing an operation on it. A data bus is the pathway through which data is transferred from MPU to memory and vice versa. The control bus carries a control information between the MPU and other components of the embedded processor. This control information carries control signals that indicate the status of the various components.

#### 2.2.5 Supporting Devices

Apart from the various modules discussed above an embedded system may require additional modules to successfully accomplish its tasks. For instance, some of the most commonly integrated modules into embedded processors are Digitalto-Analogue Converter (DAC) [38], Analogue-to-Digital Converter (ADC) [39], serial and parallel ports, timer, etc. The DAC and ADC convert digital signal to analogue and vice versa respectively. This helps the processor to interface with the external world and other electronic equipments more easily. The serial and parallel ports enable the processor to send and receive data either serially or in parallel. A timer allows the processor to measure the precise execution of selected tasks. Sometimes a processor may also have subsidiary MPUs, called **co-processors**, which generally help the main processor with heavy arithmetic and logic operations such as those used in cryptographic operations [40].

### 2.3 Characteristics of Embedded Processors

The heterogeneity of embedded systems provide engineers with a new set of challenges. As in many areas in engineering, the design of embedded systems is particularly driven by cost/benefit trade-offs. Furthermore, reliability, size and time-to-market provide additional design obstacles to engineers. This can make traditional computer system design methodologies difficult to successfully apply in embedded systems. In the following sections we discuss the main design challenges of embedded systems and their classification criteria.

#### 2.3.1 Design Parameters

The uniqueness of embedded application systems makes generalisation very difficult. Nonetheless, there is a growing interest in the area of embedded systems. The most common design challenges are size, reliability, durability and cost effectiveness [41, 42]. These challenges are discussed briefly below. **Small Size and Light Weight:** Like the name implies, embedded systems are physically located inside larger electronic equipment. The size and weight of an embedded system is determined by its application area, power consumption and portability requirement. For example, smart cards are designed to be light weight and fit into a pocket. Therefore, smart card processors are designed to meet those requirements.

Safe and Reliable: Embedded systems have been used in tasks from simple temperature sensing to assisting the functionalities of human organs [43]. Although mission critical embedded systems design raise the obvious reliability concerns, unexpected or premature malfunctionality of embedded systems in applications like game boxes may result in eroding manufacturer's reputation.

Withstand Harsh Environment: Many embedded systems are designed to operate in uncontrolled environment. One of the main problem is excessive heat especially in areas that involve combustion such as missile systems and many transport systems. However, embedded systems are also designed to withstand other harsh environments, like vibration, shock, water, corrosion, fire and other physical abuses.

**Cost Sensitivity:** Although system designers of all types of electronic devices or integrated circuits talk the importance of cost effectiveness, the sensitivity changes dramatically when it comes to embedded devices. One of the reasons is, embedded devices are deployed in mass and for a specific purpose. For instance, low-end embedded systems used to monitor environmental changes in agricultural farms [44].

#### 2.3.2 Classification

Embedded systems can be categorised into different classes based on their attributes. These attributes include the manufacturer company, architectural design, processing size, memory layout and instruction set. Fig. 2.2 illustrates the classification of embedded systems based on these attributes.

One category of embedded devices is based on the processing size of the embedded processor. The size refers to the number of bits that the processor can handle at a given time. In modern embedded systems the lowest number of bits that the processor handles is 8 bits and the highest can go up to 32/64 bits. All embedded systems have a memory where they save the program instructions and other data. If the memory module is integrated inside a single chip with the other processor modules it is known as Embedded Memory otherwise External Memory embedded system. Every embedded system have a certain set of instructions that can be used to program the processor to perform desired operation. Embedded systems with a *Reduced Instruction Set Computer* (RISC) [45] architecture use simple, single clock cycle instructions. However, for specific tasks, the number of instructions per application can be reduced by having multiple operations within a single instruction which lasts for several clock cycles. This gives a Complex Instruction Set Computer (CISC) [46] architecture. For example, a CISC processor needs only one instruction to multiply two memory contents whereas a RISC processor needs four to perform the same task. Details of this example is presented in Table 2.1.

| $\mathbf{mul} \text{ mem-loc1}, \text{ mem-loc2}$ | load a, mem-loc1        | a $\leftarrow$ mem-loc1;        |

|---------------------------------------------------|-------------------------|---------------------------------|

|                                                   | <b>load</b> b, mem-loc2 | $b \leftarrow \text{mem-loc2};$ |

|                                                   | <b>mul</b> a, b         | $a \leftarrow a^*b;$            |

|                                                   | store mem-loc1, a       | mem-loc1 $\leftarrow$ a;        |

Table 2.1: CISC, RISC and equivalent Pseudo- Code for Multiplying two Memory Contents

Apart from the CISC and RISC architectures, an embedded system is said to have a *Application Specific Instruction Set Computer* (ASIC) [47] architecture if its processing unit and instruction set are customised to do a specific type of job. Another classification criteria is the general architecture of the embedded processor. The two most common embedded architectures are the *von Neumann* and *Harvard* architectures. Those based on the von Neumann architecture [48, 49] have a single data bus for fetching program instructions and program data. Both

the program instructions and data are stored in a common main memory. When the processor has to perform a task, it fetches the instruction first and then the data associated with it. Harvard architecture processors use separate buses to access the program's instructions and data. Such a configuration allows parallel memory access to occur. The processor can fetch both the next instruction and its data simultaneously while executing the current instruction. This generally leads to improved performance. The final category criteria is the manufacturer company. In this case the processors are simply known by the name of the company that manufactured them.

## 2.4 Application Development Tools